## Computer Science Department Technical Report University of California Los Angeles, CA 90024-1596

HIGH-PERFORMANCE FAULT-TOLERANT VLSI SYSTEMS USING MICRO ROLLBACK

M. Tremblay

September 1991 CSD-910062

### UNIVERSITY OF CALIFORNIA

## Los Angeles

# High-Performance Fault-Tolerant VLSI Systems Using Micro Rollback

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy in Computer Science

by

Marc Tremblay

© Copyright by

Marc Tremblay

1991

The dissertation of Marc Tremblay is approved.

Milos D. Ercegovac

Yuval Tamir, Committee Chair

University of California, Los Angeles 1991

To Alexandra who shared this experience with love, understanding and belief.

A mes parents, pour m'avoir fait découvrir les nombreuses facettes de la vie.

## **Table of Contents**

| Chapter One - Introduction                                  | 1  |

|-------------------------------------------------------------|----|

| 1.1. Applications of Micro Rollback                         | 3  |

| 1.2. Implementation of Micro Rollback                       | 9  |

| 1.3. Organization of this Work                              | 9  |

| Chapter Two - Previous Work                                 | 12 |

| 2.1. Error Detection                                        | 12 |

| 2.2. MPCU with Concurrent Error Detection                   | 14 |

| 2.3. Error Recovery                                         | 17 |

| 2.3.1. Forward Error Recovery                               | 17 |

| 2.3.2. Backward Error Recovery                              | 19 |

| 2.3.3. Instruction Retry                                    | 22 |

| 2.4. Related Work                                           | 27 |

| Chapter Three - Error Detection and Correction Circuits for |    |

| VLSI Processors                                             | 31 |

| 3.1. Implementation of Multi-Input XOR Gates                | 33 |

| 3.1.1. Static Implementation                                | 36 |

| 3.1.2. Chains of Switching Cells                            | 38 |

| 3.1.2.1. N-Chain                                            | 40 |

| 3.1.2.2. N-Precharged Chain                                 | 43 |

| 3.1.2.3. P-Precharged Chain                                 | 46 |

| 3.1.2.4. Dual-chain                                           | 48 |

|---------------------------------------------------------------|----|

| 3.1.2.5. Switching Cells With Sense Amplifiers                | 49 |

| 3.1.2.6. Metrics of the Parity Circuits                       | 52 |

| 3.1.3. Influence of the Data Bus Pitch on the XOR Gate Design | 53 |

| 3.2. Error Correction Circuitry                               | 57 |

| 3.3. Duplication and Comparison                               | 64 |

| 3.3.1. Compression                                            | 64 |

| 3.3.2. Comparison                                             | 67 |

| 3.4. EDC Circuits and the Micro architecture of a Processor   | 68 |

| 3.5. Summary                                                  | 70 |

| Chapter Four - Micro Rollback                                 | 72 |

| 4.1. Definition of Micro Rollback                             | 72 |

| 4.1.1. Micro Rollback in Virtual and Real Time                | 74 |

| 4.2. Support for Micro Rollback in a VLSI RISC Processor      | 80 |

| 4.2.1. Micro Rollback of the Register File                    | 82 |

| 4.2.1.1. High-level Description                               | 82 |

| 4.2.1.2. Implementation of the Register File and DWB          | 84 |

| 4.2.1.4. Pipeline Organization                                | 89 |

| 4.2.1.5. Performance and Area Overheads                       | 90 |

| 4.2.1.6. Timing                                               | 91 |

| 4.2.1.7. Area Overhead                                        | 92 |

| 4.2.2. Comparison of the DWB with other Methods               | 93 |

| 4.2.3. Detection and Correction of Errors in the Register File | 100 |

|----------------------------------------------------------------|-----|

| 4.2.3.1. Duplex Processors                                     | 101 |

| 4.2.3.2. Use of Error Correcting Codes                         | 101 |

| 4.2.4. Micro Rollback of Individual State Registers            | 102 |

| 4.2.5. Micro Rollback for the PC Unit                          | 104 |

| 4.2.5.1. Error Detection for State Registers                   | 106 |

| 4.2.6. A DWB for Infrequently Modified Registers               | 107 |

| 4.3. System Issues in the use of Micro rollback                | 112 |

| 4.3.1. Micro Rollback and Cache Memory                         | 113 |

| 4.3.2. Micro Rollback and Main Memory                          | 115 |

| 4.4. Micro Rollback in a Multiprocessor Environment            | 116 |

| 4.5. Summary and Conclusions                                   | 120 |

| Chapter Five - Micro Rollback for High-Performance Multi-      |     |

| Module VLSI Systems                                            | 122 |

| 5.1. Micro Rollback of Multi-Module Systems                    | 123 |

| 5.2. Transducers                                               | 127 |

| 5.3. Micro Rollback in Bus-Connected Systems                   | 131 |

| 5.4. Summary and Conclusions                                   | 134 |

| Chapter Six - Interactions with Modules Outside of the Micro   |     |

| Rollback Domain                                                | 136 |

| 6.1. Hybrid Systems                                            | 137 |

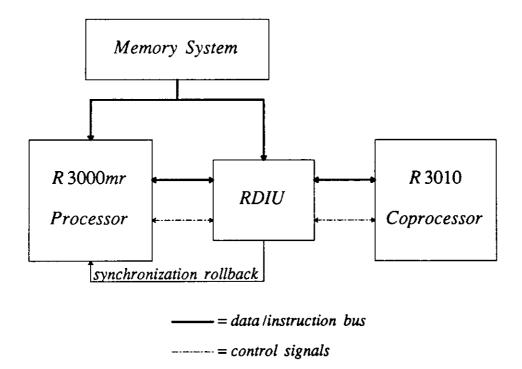

| 6.2. Rollback Domain Interface Unit                            | 139 |

| 6.3. Cache/Memory System Outside the Rollback Domain           | 141 |

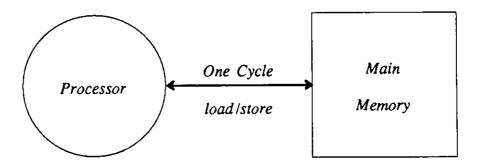

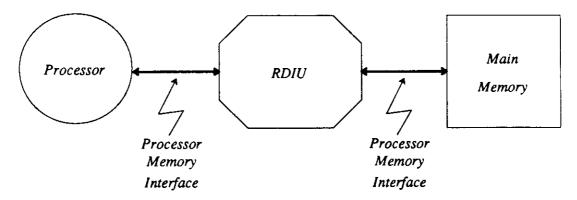

| 6.3.1. Processor and Single Cycle Memory                           | 142 |

|--------------------------------------------------------------------|-----|

| 6.3.2. Processor and Memory with Wait States                       | 150 |

| 6.3.3. Processor and Memory with Burst Access Mode                 | 153 |

| 6.3.4. Processor and Memory with Pipelined Accesses                | 156 |

| 6.3.5. General RDIU for a Processor-Memory System                  | 165 |

| 6.4. Loosely-Coupled Coprocessors and Micro Rollback               | 166 |

| 6.5. Tightly Coupled Coprocessors                                  | 170 |

| 6.5.1. The R3010 Coprocessor Operation                             | 171 |

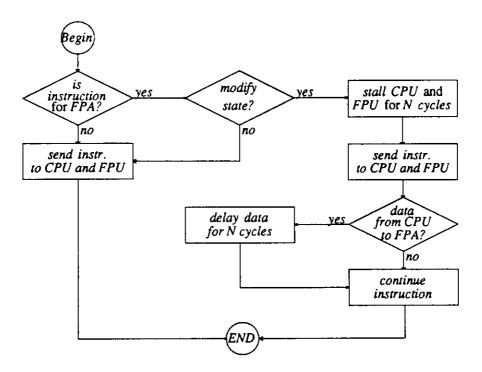

| 6.5.2. Individual FPA Instructions Intercepted                     | 172 |

| 6.5.3. Non-damaging FPA Instructions Sent Directly                 | 179 |

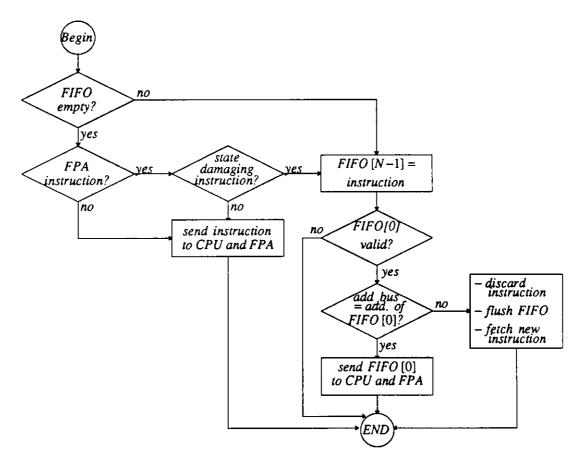

| 6.5.4. Instruction Prefetch Buffer                                 | 181 |

| 6.6. Conclusion                                                    | 184 |

| Chapter Seven - Combination of Micro Rollback with Speed-Up        |     |

| Techniques                                                         | 187 |

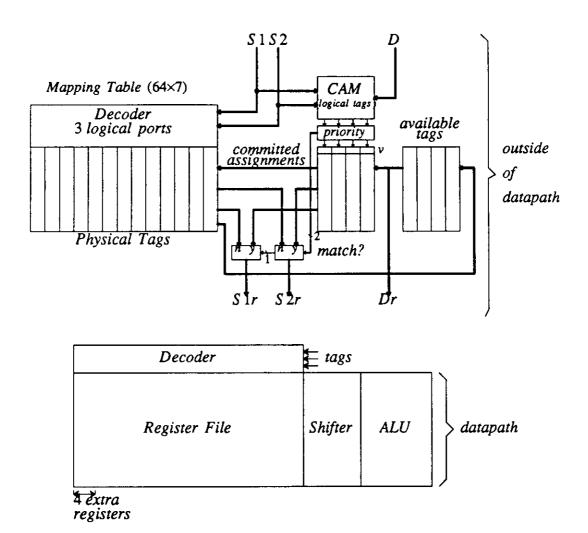

| 7.1. Micro Rollback and Register Renaming                          | 189 |

| 7.1.1. Micro Rollback of a Simple Processor Using Register         |     |

| Renaming                                                           | 191 |

| 7.1.2. Micro Rollback and Register Renaming for a Superscalar      |     |

| Processor                                                          | 204 |

| 7.2. Integrating Support for Micro Rollback and Precise Interrupts | 211 |

| 7.2.1. Rollback of the RSR and RB Using Multiple DWBs              | 214 |

| 7.2.2. Rollback of RSR and RB Using Marked Entries                 | 220 |

| 7.3. Combination of Rollback with Several Speed-Up Techniques      | 227 |

| 7.4. Rollback of Pipelined Functional Units with Long Latencies | 233 |

|-----------------------------------------------------------------|-----|

| 7.4.1. Elimination of the Result Shift Register                 | 236 |

| 7.5. Conclusion                                                 | 237 |

| Chapter Eight - Summary                                         | 239 |

| Bibliography                                                    | 242 |

# List of Figures

| 1.1 | Error Detection                                             | 2  |

|-----|-------------------------------------------------------------|----|

| 1.2 | Application of parallel error detection                     | 4  |

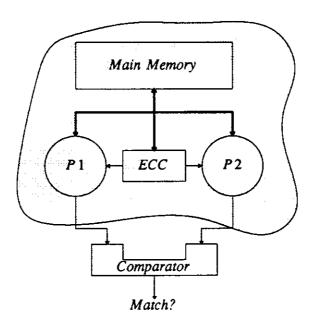

| 1.3 | Processors operating in duplex mode                         | 5  |

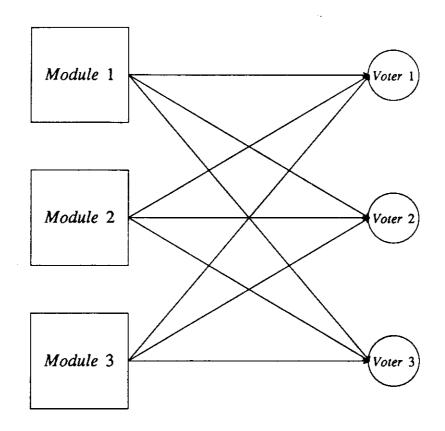

| 1.4 | Processors running in Triple Modular Redundancy (TMR)       | 6  |

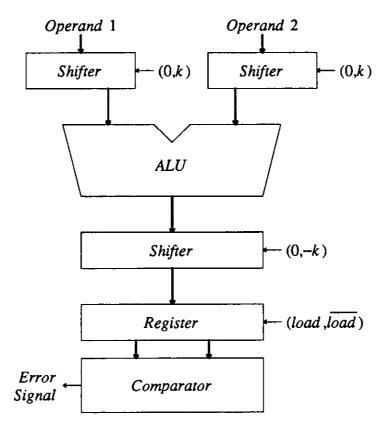

| 1.5 | Error detection by Recomputing with Shifted Operands (RESO) | 7  |

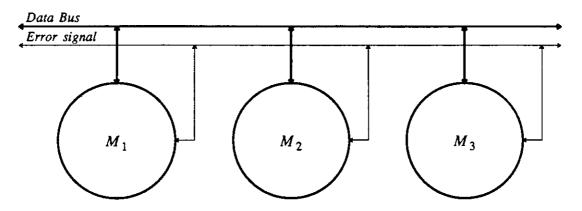

| 1.6 | System with Self-Checking Modules                           | 8  |

| 2.1 | Triple Modular Redundancy with Triplicate Voters            | 18 |

| 2.2 | Forward Error Recovery                                      | 18 |

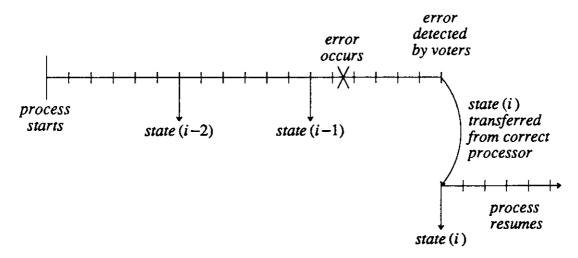

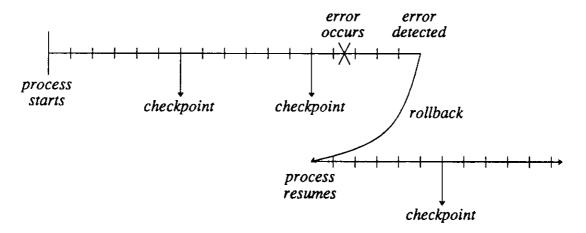

| 2.3 | Checkpointing and Recovery Through Rollback                 | 20 |

| 2.4 | Recovery for Small Error Detection Latency                  | 21 |

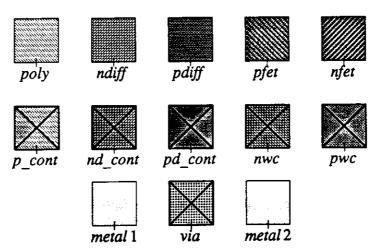

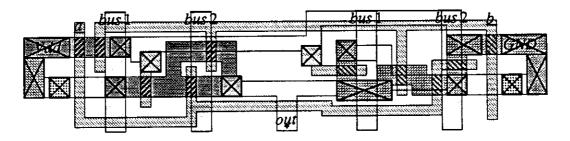

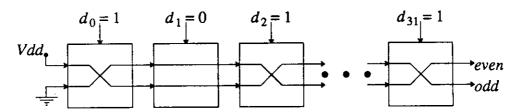

| 3.1 | Representation of VLSI Layers                               | 33 |

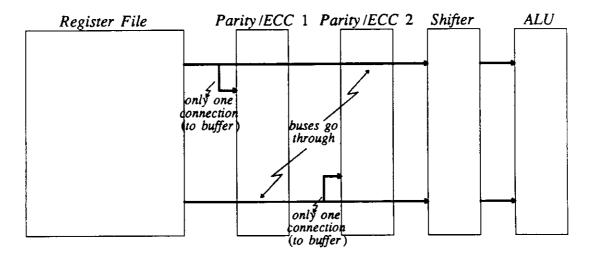

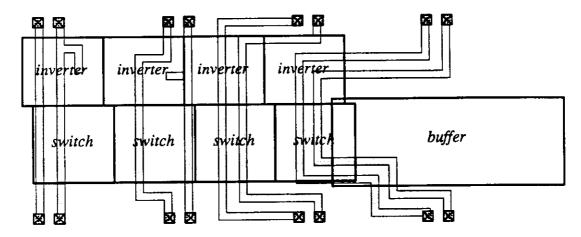

| 3.2 | Buses Routed Over Parity/ECC Circuitry                      | 35 |

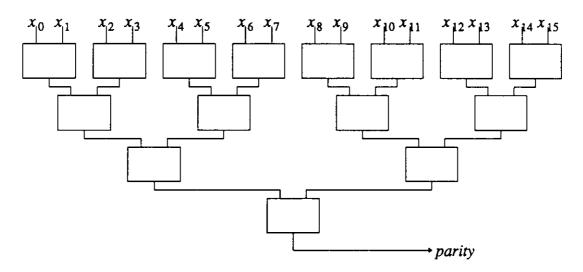

| 3.3 | 16-Input Tree of XORs                                       | 36 |

| 3.4 | Compact Layout of an XOR-Tree                               | 37 |

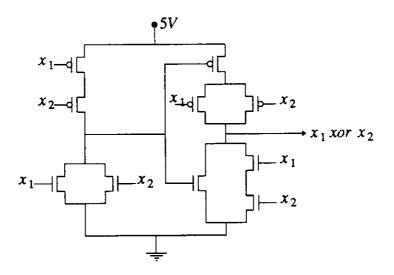

| 3.5 | Static XOR                                                  | 38 |

| 3.6 | Layout of a Static XOR Gate                                 | 38 |

| 3.7 | A Chain of Switching Cells                                  | 39 |

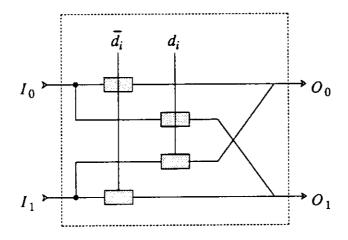

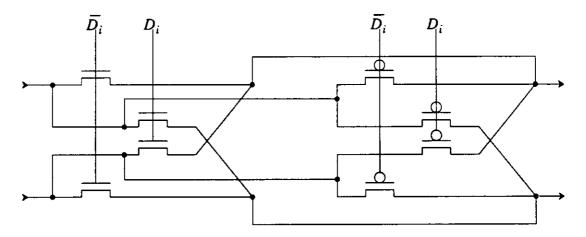

| 3.8 | A Switching Cell                                            | 39 |

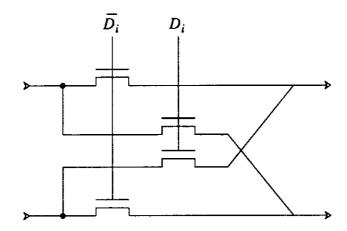

| 39  | A Switching Cell Implemented with N-Transistors             | 40 |

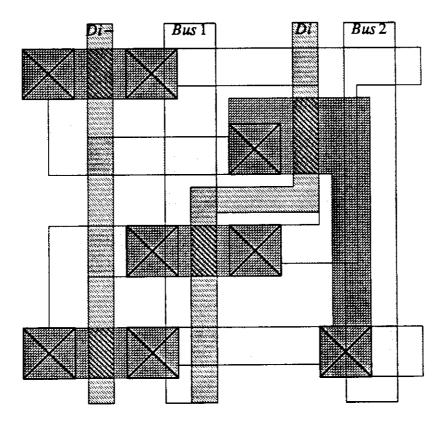

| 3.10 Layout of a Switching Cell Implemented with N-Transistors | 42 |

|----------------------------------------------------------------|----|

| 3.11 Layout of a Sub-Chain of 4 Switching Cells                | 43 |

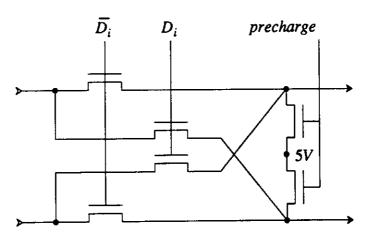

| 3.12 N-Precharged XOR Cell                                     | 43 |

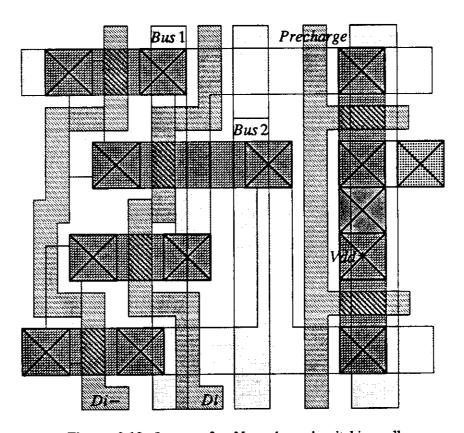

| 3.13 Layout of an N-Precharged Switching Cell                  | 44 |

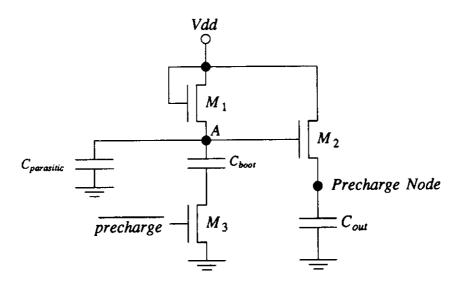

| 3.14 Bootstrap Circuitry                                       | 45 |

| 3.15 P-Precharged XOR Cell                                     | 47 |

| 3.16 Layout of a P-Precharged Switching Cell                   | 47 |

| 3.17 Dual-Chain XOR Cell                                       | 48 |

| 3.18 Layout of a Dual-Chain Switching Cell                     | 49 |

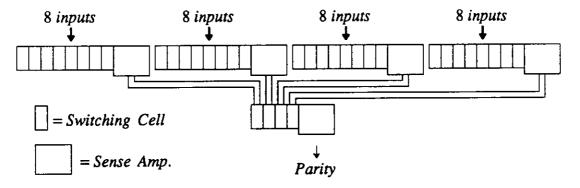

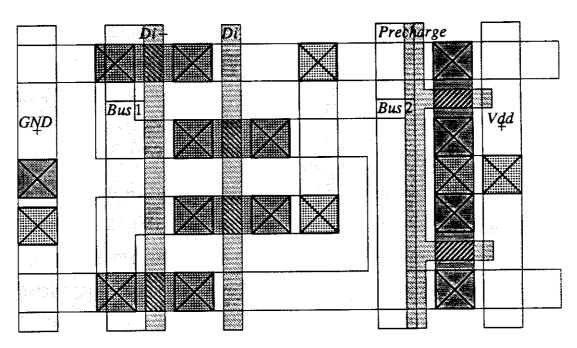

| 3.19 Tree of 8-Input XOR with Sense-Amp.                       | 49 |

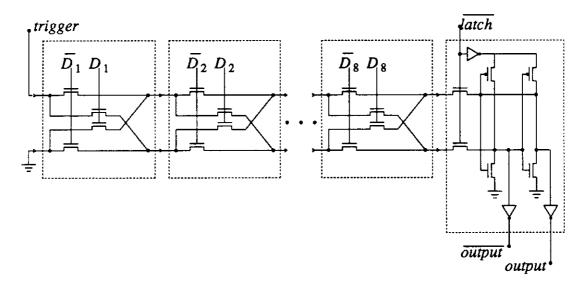

| 3.20 A Chain of XORs with Sense Amplifier                      | 50 |

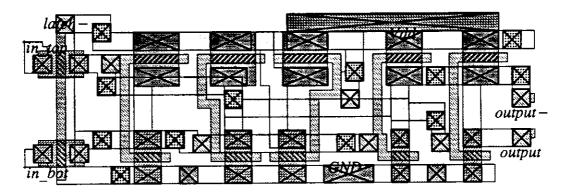

| 3.21 Layout of the Sense-Amplifier                             | 51 |

| 3.22 P-Precharged XOR Cell for a Larger Pitch                  | 55 |

| 3.23 Dual Chain of Switching Cells Laid Out Horizontally       | 56 |

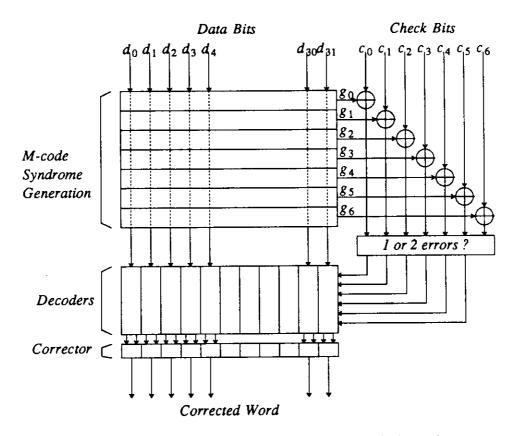

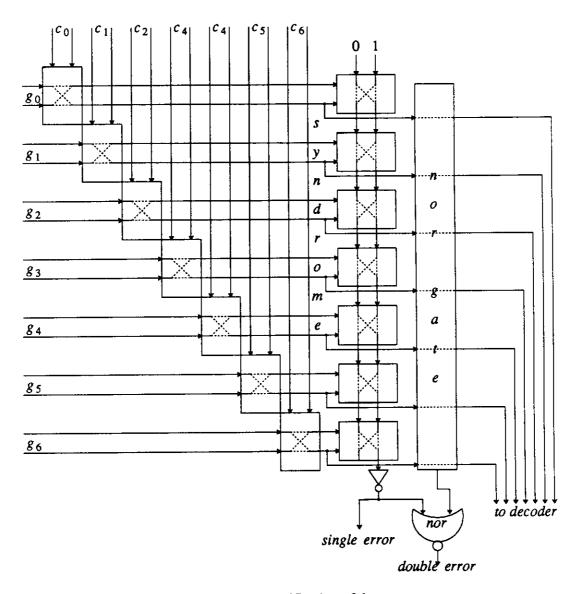

| 3.24 M-Code Parity Check Matrix (PCM)                          | 58 |

| 3.25 Error Detection and Correction of a 32-bit Word           | 59 |

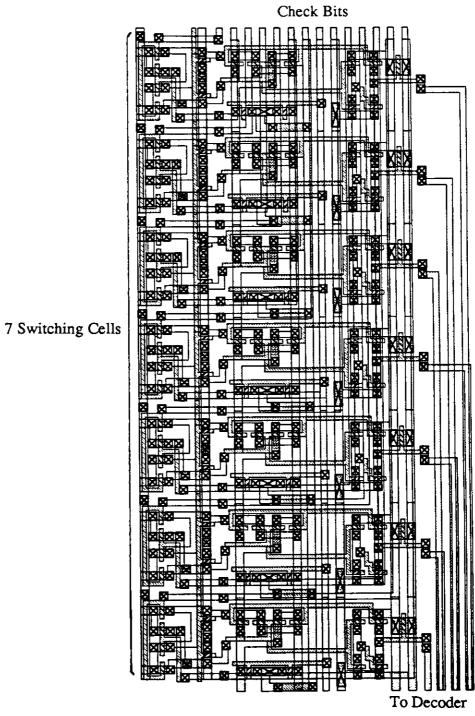

| 3.26 Identification of the Error                               | 61 |

| 3.27 Layout for Error Identification                           | 62 |

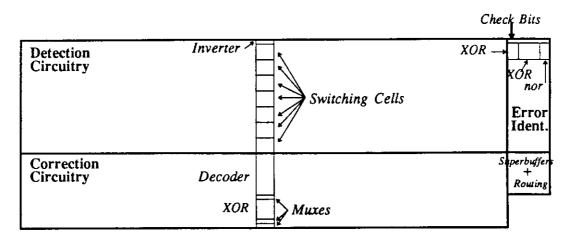

| 3.28 Floorplan for EDC                                         | 64 |

| 3.29 Processors in Duplex Mode                                 | 65 |

| 3.30 Interlaced Parity used for Compression                    | 66 |

| 3.31 Slice of the Data Compression Circuit                     | 67 |

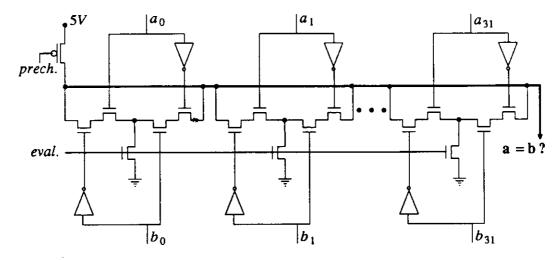

| 3.32 A 32-input Comparator                               | 68  |

|----------------------------------------------------------|-----|

| 4.1 Micro Rollback of a Module                           | 73  |

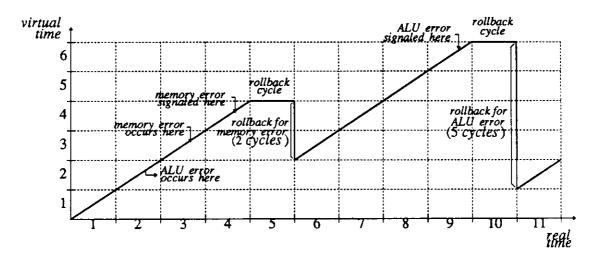

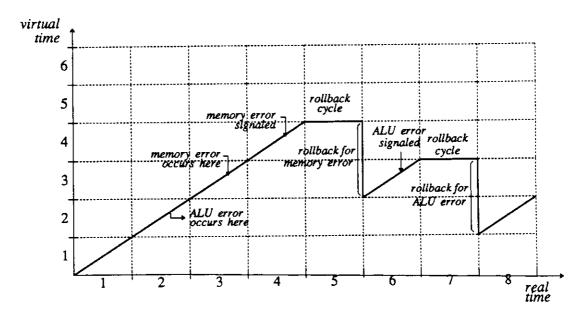

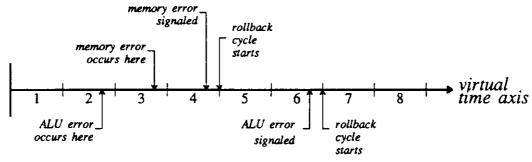

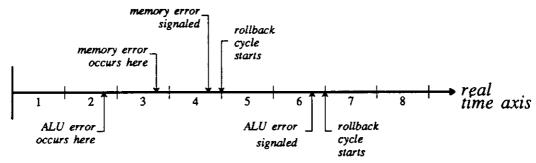

| 4.2 Micro Rollback in a Virtual Time vs. Real Time Graph | 75  |

| 4.3 Homogeneous System with Two Checkers                 | 75  |

| 4.4 Overlapping Rollbacks in Virtual Time                | 77  |

| 4.5 Heterogeneous System with Two Checkers               | 78  |

| 4.6 Overlapping Rollbacks in Real Time                   | 80  |

| 4.7 Comparison of Real Time and Virtual Time Frames      | 81  |

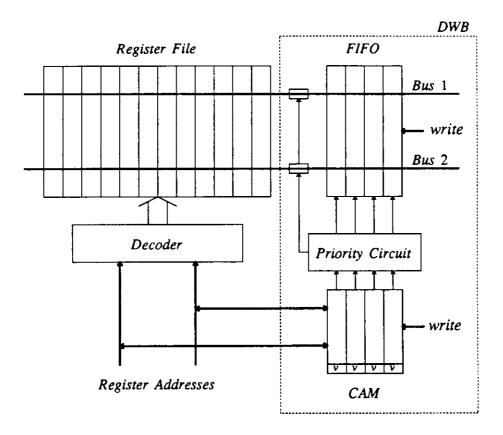

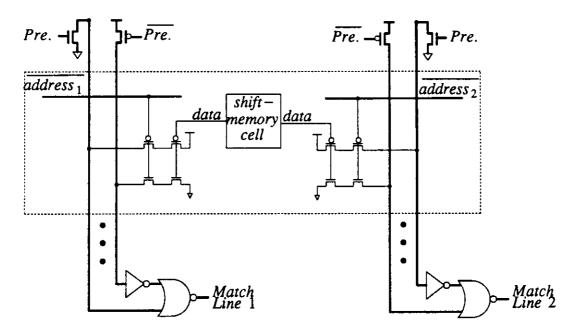

| 4.8 A Register File with Support for Micro Rollback      | 83  |

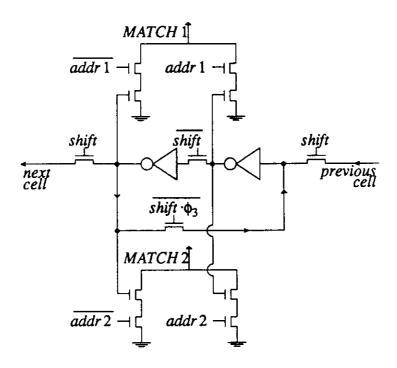

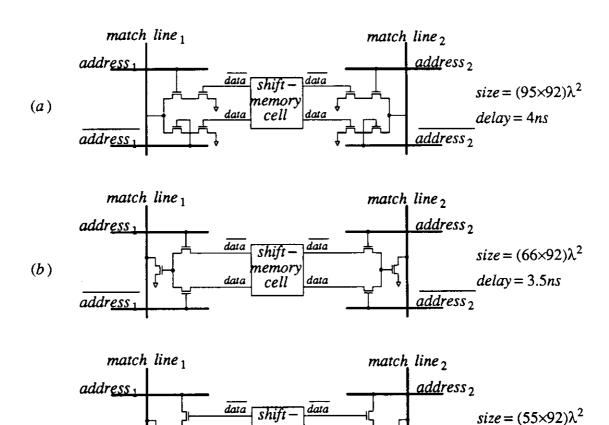

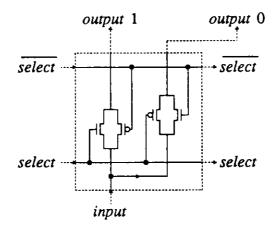

| 4.9 A FIFO/CAM Cell for the Delayed-Write Buffer         | 85  |

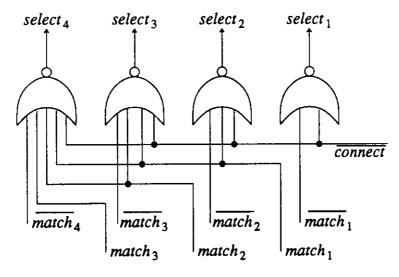

| 4.11 Layout of the FIFO/CAM Cell                         | 86  |

| 4.13 Comparison of Three Different CAM Circuits          | 88  |

| 4.14 CAM Cell Optimized for Reducing Vertical Dimension  | 89  |

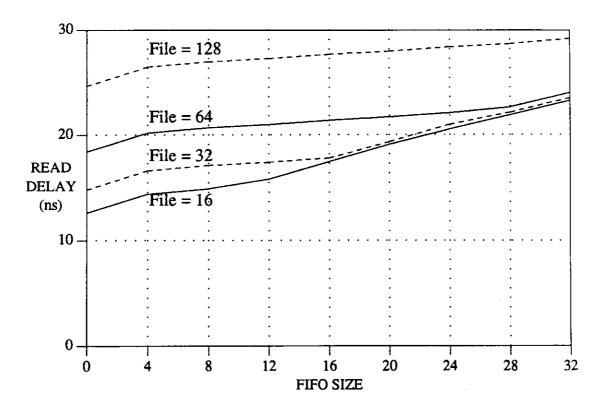

| 4.15 Read Delay Overhead                                 | 91  |

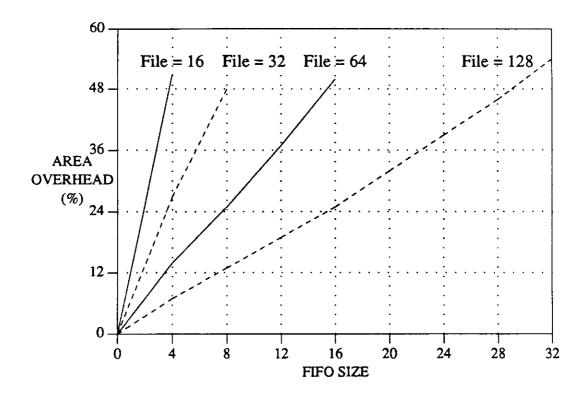

| 4.16 Area Overhead                                       | 93  |

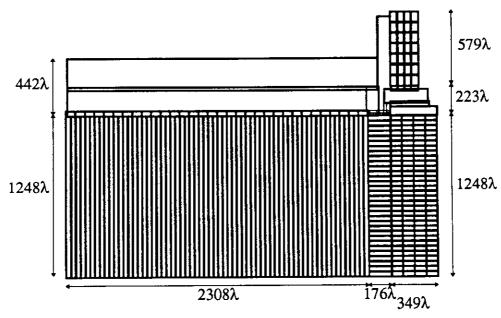

| 4.17 Register File and DWB Layout                        | 94  |

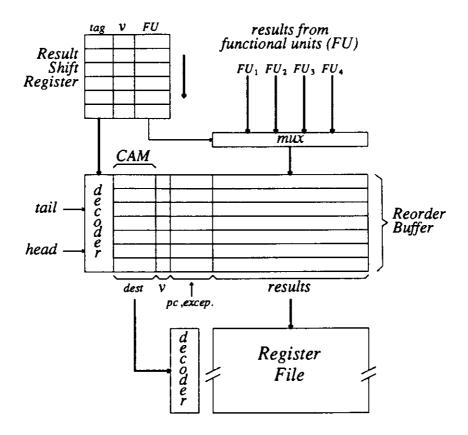

| 4.18 Reorder buffer with result shift register           | 95  |

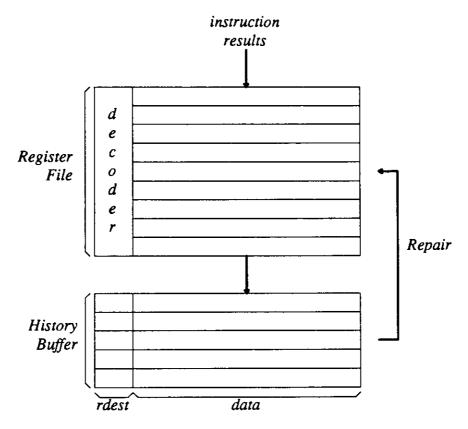

| 4.19 History Buffer                                      | 97  |

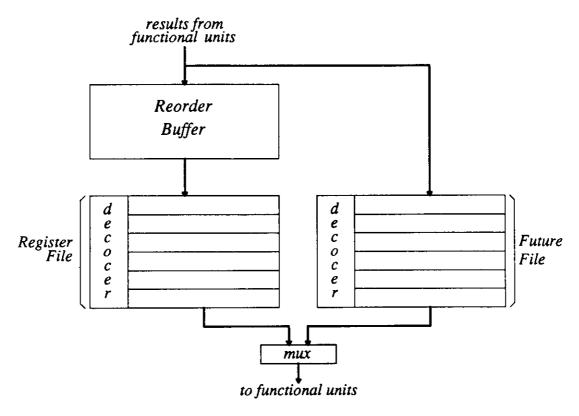

| 4.20 Future File                                         | 98  |

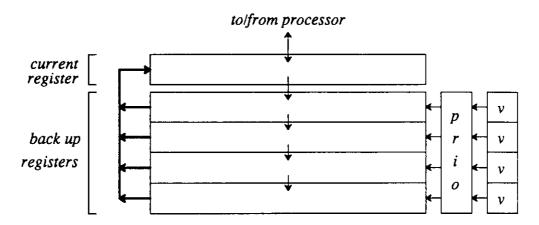

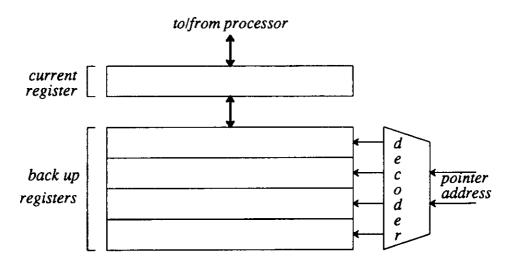

| 4.21 FIFO Rollback for Individual State Registers        | 103 |

| 4.22 RAM rollback for Individual State Registers         | 103 |

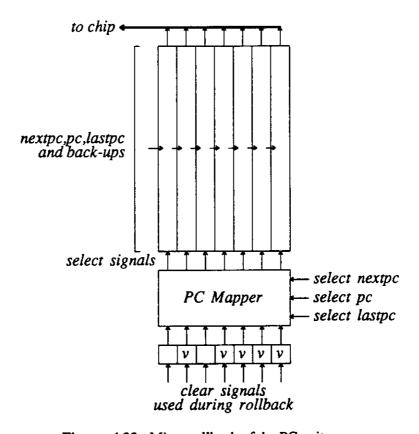

| 4.23 Micro Rollback of the PC Unit                       | 105 |

| 4.24 Mapper Circuitry for the PC Unit                  | 106 |

|--------------------------------------------------------|-----|

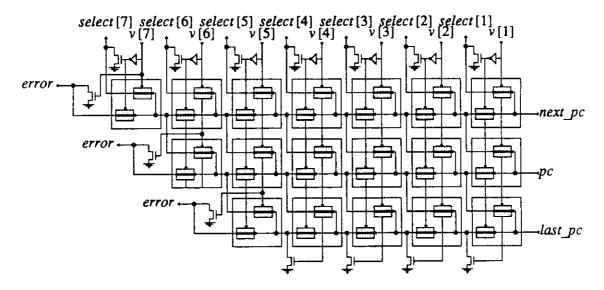

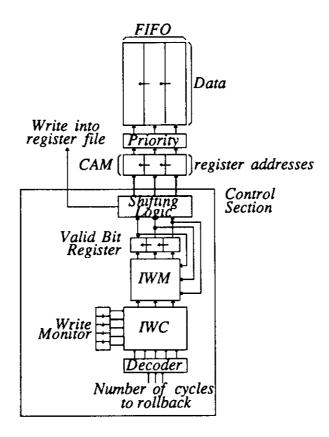

| 4.25 DWB for Infrequently Modified Registers           | 108 |

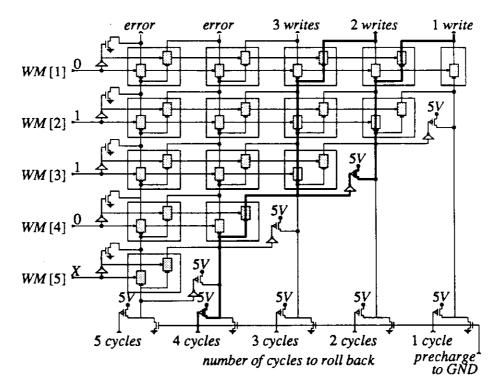

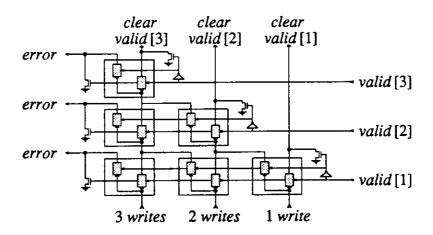

| 4.26 Invalidate Write Counter (IWC)                    | 109 |

| 4.27 Basic Cell for Invalidate Write Counter           | 110 |

| 4.28 Invalidate Write Mapper (IWP)                     | 110 |

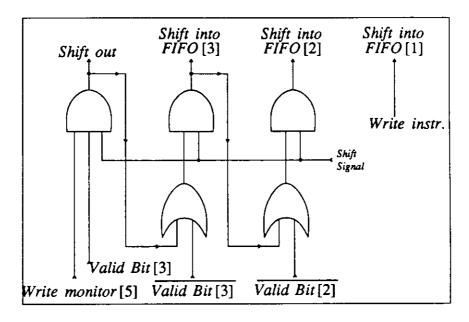

| 4.29 Control Circuitry for Shifting the DWB            | 111 |

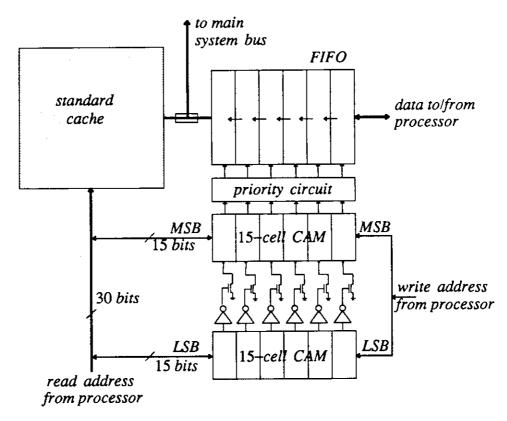

| 4.30 Cache with Support for Micro Rollback             | 114 |

| 4.31 Store — Load Problem                              | 117 |

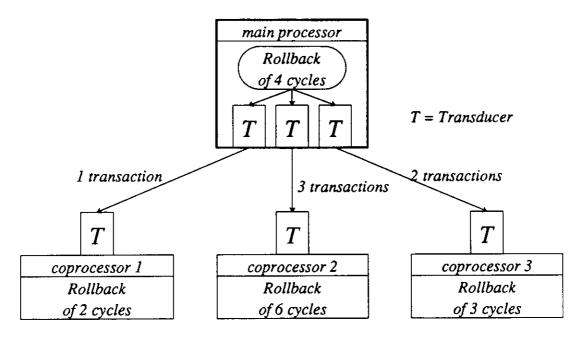

| 5.1 Micro Rollback in a Synchronous System             | 124 |

| 5.2 Micro Rollback in an Asynchronous System           | 125 |

| 5.3 Synchronization Through Transducers                | 126 |

| 5.4 Transducers in an Asynchronous Multi-Module System | 127 |

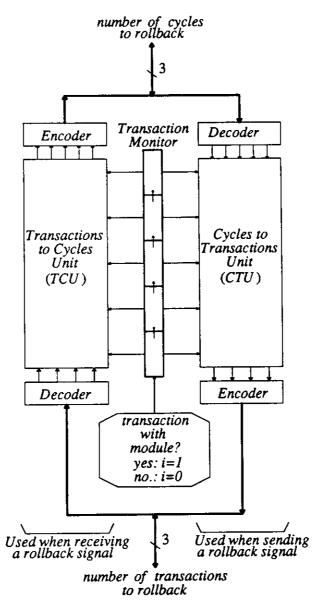

| 5.5 Transducer                                         | 128 |

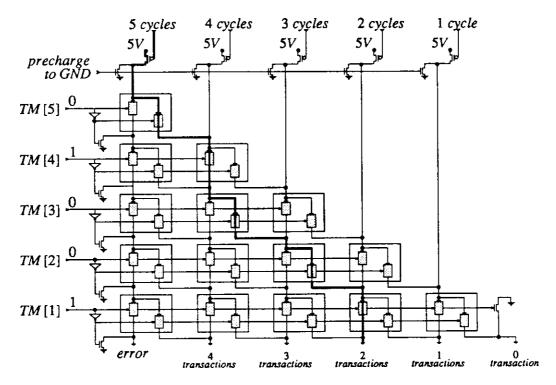

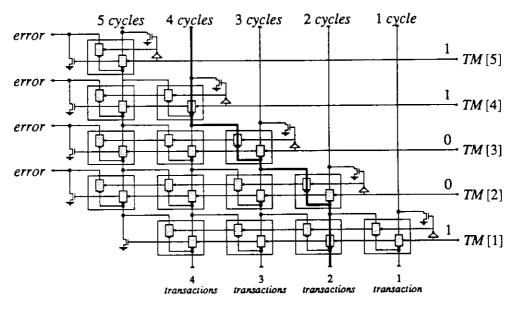

| 5.6 A cycles to transactions unit (CTU)                | 129 |

| 5.7 A transactions to cycles unit (TCU)                | 130 |

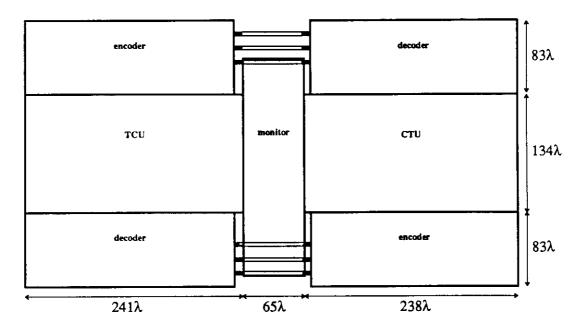

| 5.8 Layout of a Transducer                             | 131 |

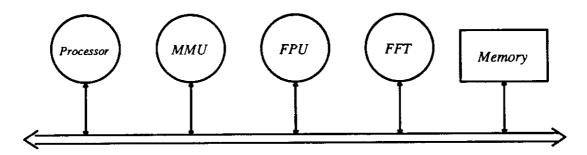

| 5.9 Bus-Based Multi-Module System                      | 132 |

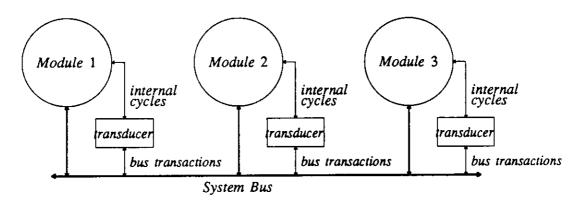

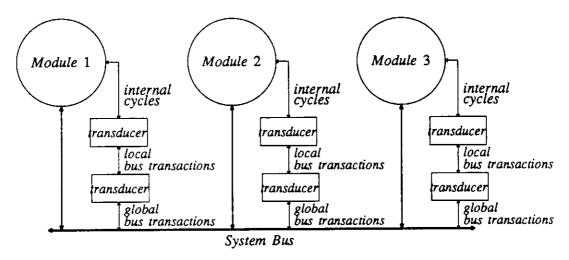

| 5.10 Elimination of the Domino Effect                  | 133 |

| 5.11 Optimized Elimination of the Domino Effect        | 134 |

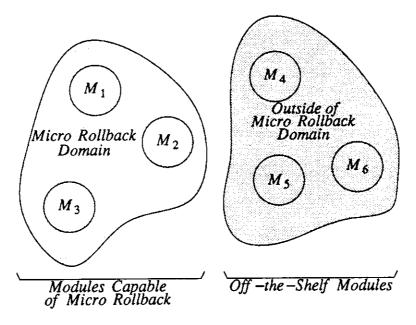

| 6.1 Classification of Modules in a System              | 136 |

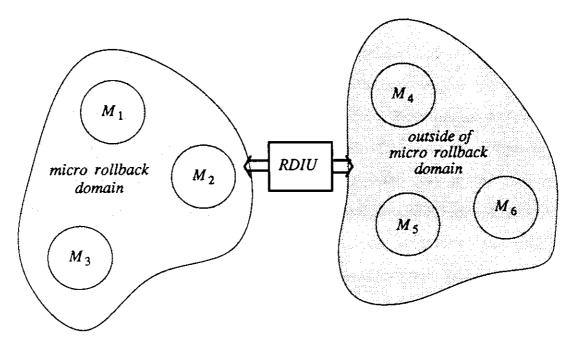

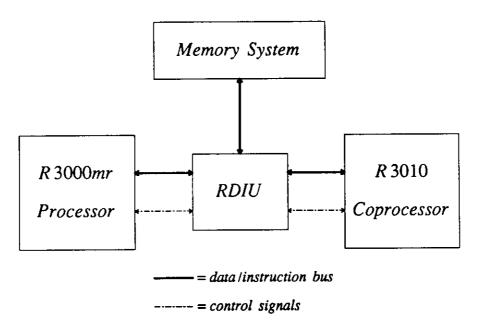

| 6.2 Insertion of an RDIU in the Communication Path     | 140 |

| 6.4. Single Cycle Communication                        | 142 |

| 6.5 RDIU Between Processor — Memory          | 143 |  |  |  |  |

|----------------------------------------------|-----|--|--|--|--|

| 6.6 General RDIU for Simple Memory           |     |  |  |  |  |

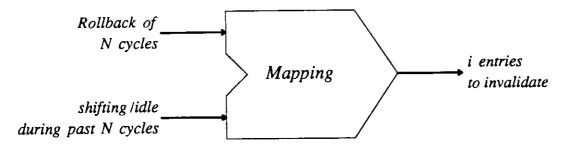

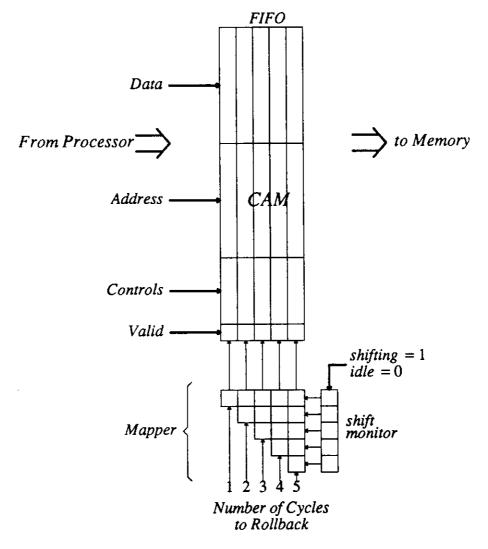

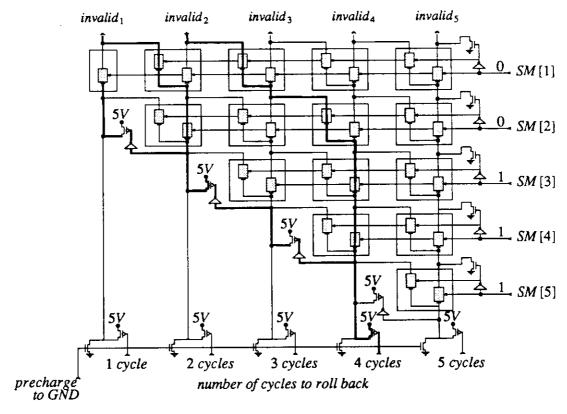

| 6.7 Mapping Between Cycles and Invalidates   |     |  |  |  |  |

| 6.8 Block Diagram of the Mapping Circuitry   |     |  |  |  |  |

| 6.9 Store Mapper                             |     |  |  |  |  |

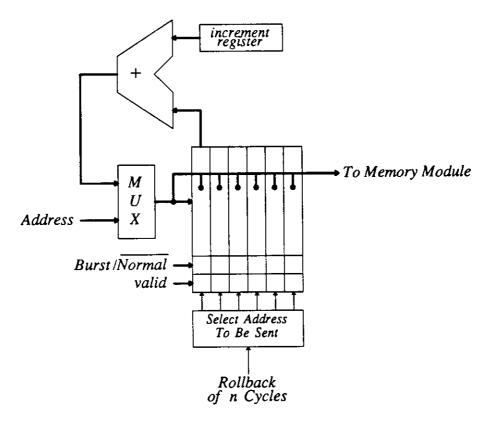

| 6.10 Rollback During a Burst Load            |     |  |  |  |  |

| 6.11 Logic for Burst Load                    |     |  |  |  |  |

| 6.12 Pipelined Memory Subsystem              | 157 |  |  |  |  |

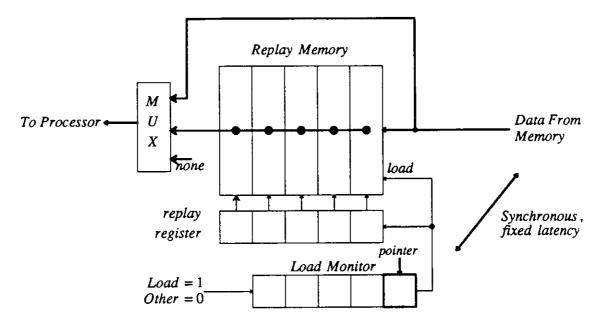

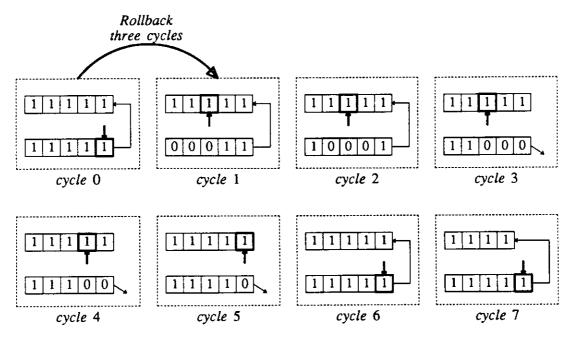

| 6.13 Shift register for Pending Loads        | 159 |  |  |  |  |

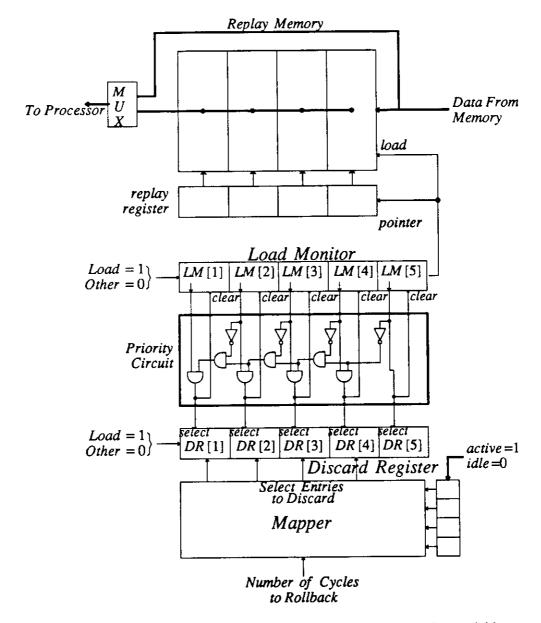

| 6.15 Loads with Variable Latencies           | 162 |  |  |  |  |

| 6.16 Out-of-Order Loads                      | 164 |  |  |  |  |

| 6.17 Out-of-Order Loads                      | 165 |  |  |  |  |

| 6.18 Complex RDIU                            |     |  |  |  |  |

| 6.19 N-Deep FIFO Interface                   |     |  |  |  |  |

| 6.20 RDIU Intercepts Instructions            | 172 |  |  |  |  |

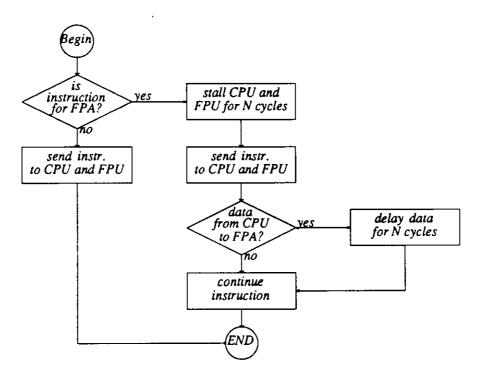

| 6.21 RDIU Intercept Flowchart                | 173 |  |  |  |  |

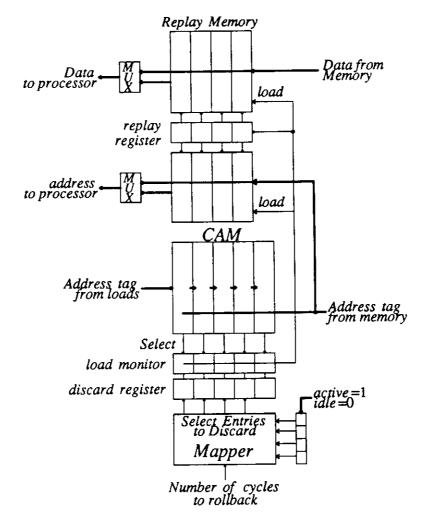

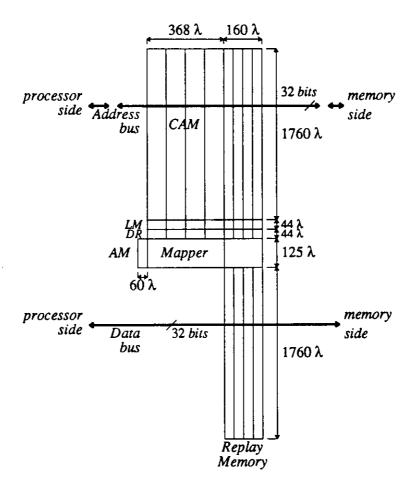

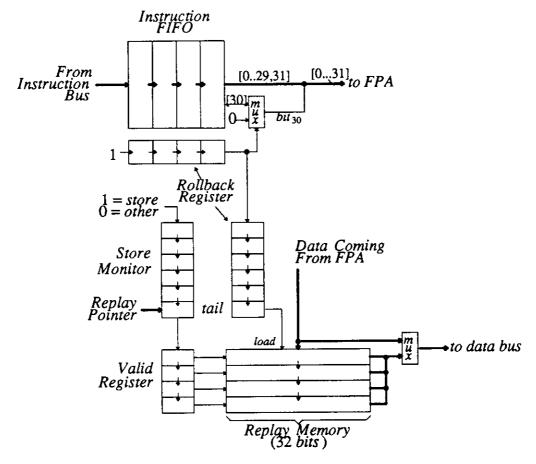

| 6.22 Replaying Circuitry                     | 174 |  |  |  |  |

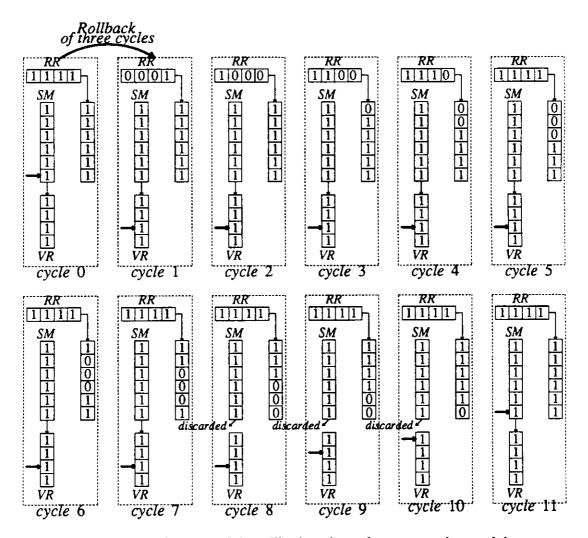

| 6.23 Contents of RR, SM, and VR              | 177 |  |  |  |  |

| 6.24 Flowchart for Optimized Solution        | 180 |  |  |  |  |

| 6.25 Flowchart for Complex Solution          | 182 |  |  |  |  |

| 6.26 Optimized Solution Circuit              | 183 |  |  |  |  |

| 7.1 Micro Rollback through Register Renaming | 193 |  |  |  |  |

| 7.2 Optimized Rollback through Register Renaming             | 195 |

|--------------------------------------------------------------|-----|

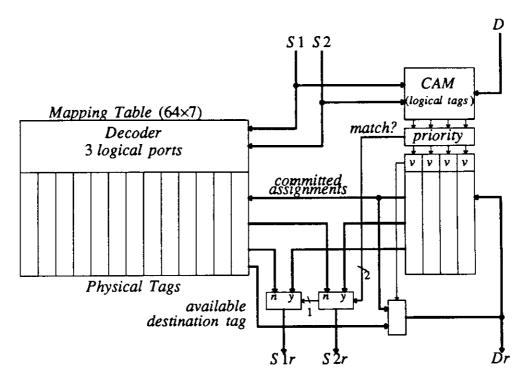

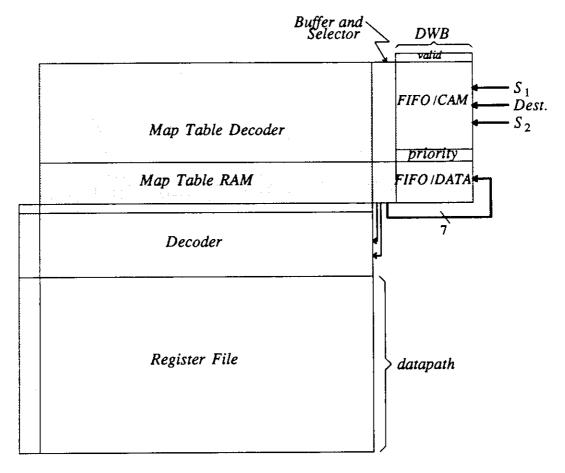

| 7.3 Layout of Register Renaming Circuitry                    | 196 |

| 7.4 Register Renaming Scheme for the IBM RS/6000             | 206 |

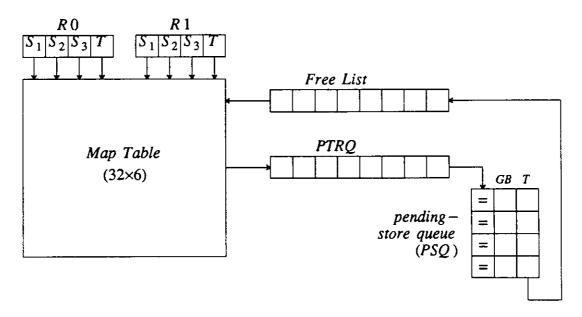

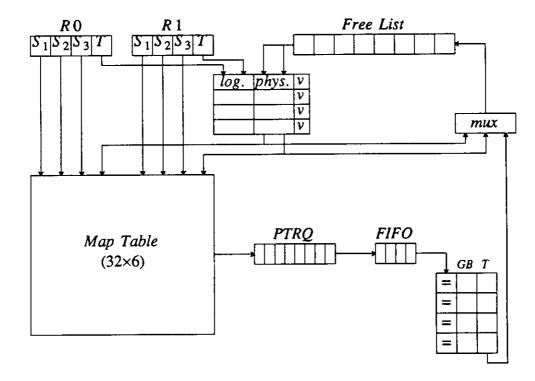

| 7.5 New Structure for RS/6000                                | 207 |

| 7.6 Register Tag Released After a Long Latency               | 208 |

| 7.7 New Pending Target Return Queue (PTRQ)                   | 209 |

| 7.8 Processor with Several Pipelined Functional Units        | 212 |

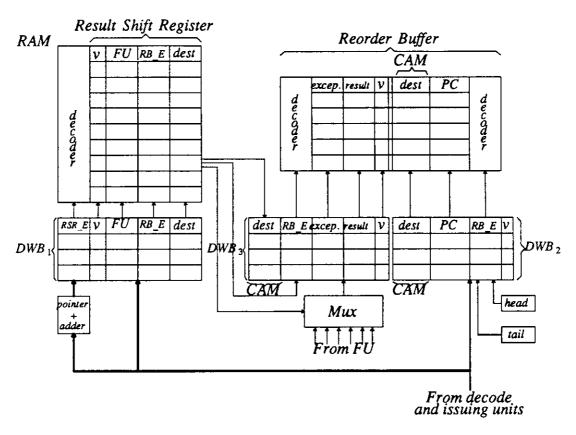

| 7.9 Result Shift Register and Reorder Buffer                 | 213 |

| 7.10 Micro Rollback Added to a Multiple Functional Unit CPU  | 214 |

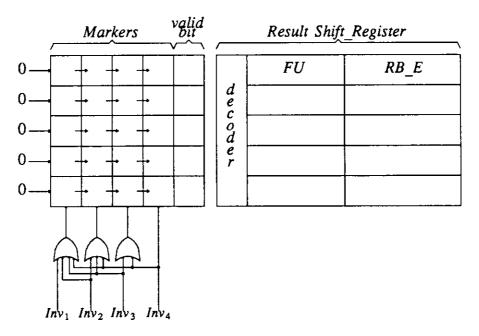

| 7.11 Four Bit Marker                                         | 220 |

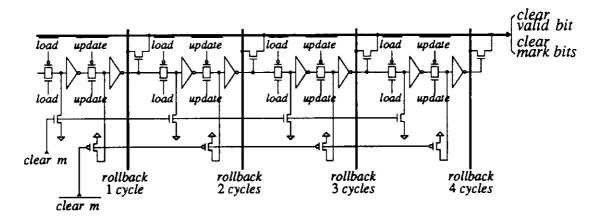

| 7.12 Mark Bits and the Clear Valid Bit Signal                | 221 |

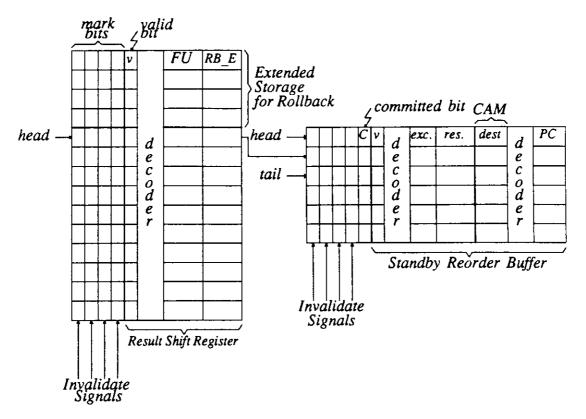

| 7.13 Marked Result Shift Register and Standby Reorder Buffer | 222 |

| 7.14 Last Mark Bit                                           | 225 |

| 7.15 Standby Reorder Buffer (SRB)                            | 229 |

| 7.16 Pipeline Usage Monitor (PUM)                            | 235 |

| 7.17 Example of a Rollback for Long Pipelines                | 236 |

## List of Tables

| 3.1 | Metrics of Parity Circuits                           | 52  |

|-----|------------------------------------------------------|-----|

| 3.2 | Comparison Register Files                            | 54  |

| 3.3 | Area and Delay for EDC                               | 60  |

| 4.1 | Comparison of State Register Rollback Methods        | 104 |

| 4.2 | The Areas of Optimized and Full DWBs                 | 112 |

| 7.1 | Formulas for Calculating Area Overhead               | 197 |

| 7.2 | Area Overhead for Rollback Through Register Renaming | 200 |

| 7.3 | Area Overhead for RSR, RB, and Three DWBs            | 218 |

| 7.4 | Area Overhead for the Marked RSR                     | 226 |

| 7.5 | Area Overhead for the SRB                            | 226 |

#### ACKNOWLEDGMENTS

Many persons have contributed to creating a positive environment which helped me produce the research described in this dissertation. I wish to express my gratitude to all of them.

My advisor, Yuval Tamir, through his dedication to research, through his desire to produce perfect papers, and through his broad knowledge of computer science, has taught me a great deal. Yuval's method of conducting research and how it relates to other fields will have a lasting impression on my future career. Yuval's comments and inputs have brought this dissertation to a level that I would not have reached on my own. Thanks, Yuval, for all the advice (generally given during one of our many "late night" discussions).

I would like to thank members of the committee for their comments on my research. More specifically Prof. David Rennels, who has always been supportive, contributed to the theory of micro rollback. Prof. Milos Ercegovac and Prof. Tomas Lang have helped me with a variety of issues during my stay at UCLA, through their teaching, their insight on research, and even with desk allocation!

This journey would not have been as significant, had I not encountered my fiancée, Alexandra, during this time. She has provided unconditional support, lots of encouragement, and also some of the much needed extra-curricular activities that kept me sane throughout these past several years of research.

My gratitude also goes out to my colleagues, Jaime Moreno, Miquel Huguet, Leon Alkalaj and Paul Tu. Our conversations, our lunches, and our more "formal" meetings during the CIGAR seminars, were all moments that I cherish. The computer science department at UCLA possesses several good people who care about the students. Verra Morgan, Roberta Nelson, Doris Sublette, and Rosemary Murphy are all dedicated to creating a pleasant environment. The help that Verra provided will never be forgotten.

I am very fortunate to have friends like Gary Park, Jeff Bixler, Robert Krasuski and Thuvan Nguyen. They kept my intellect active on topics other than computer science and kept my level of competition in a multitude of sports, quite challenging. Thanks to all of you.

I am also very grateful to my parents, my sister Luci, and my brother Rejean, who have always been there in times of need. Their support, even if sometimes taken for granted, is greatly appreciated and will never be forgotten.

My appreciation also goes to the National Research Council of Canada who supported me for four years, IBM for the Graduate Fellowship, Hughes Aircraft Company and the State of California MICRO Program who provided financial assistance for my research. Special thanks to Dr. T. Basil Smith who made the whole IBM experience an enjoyable and valuable one.

#### VITA

| October 30, 1961 | Born in Quebec, Canada                                                                                     |

|------------------|------------------------------------------------------------------------------------------------------------|

| 1984             | B.S Physics Engineering Université Laval Québec, Canada                                                    |

| 1984-1988        | National Research Council Fellowship (Canada)                                                              |

| 1985             | M.S. Computer Science University of California, Los Angeles Los Angeles, California                        |

| 1985-1991        | Teaching Assistant, Teaching Assosiate<br>University of California, Los Angeles<br>Los Angeles, California |

| 1987-1990        | Research Assistant, Research Assosiate<br>University of California, Los Angeles<br>Los Angeles, California |

| 1989-1990        | IBM Graduate Fellowship                                                                                    |

#### **PUBLICATIONS AND PRESENTATIONS**

- 1. Y. Tamir and M. Tremblay, "High-Performance Fault-Tolerant VLSI Systems Using Micro Rollback," *IEEE Transactions on Computers* 39(4), pp. 548-554 (April 1990).

- 2. Y. Tamir, M. Tremblay, and D. A. Rennels, "The Implementation and Application of Micro Rollback in Fault-Tolerant VLSI Systems," 18th Fault-Tolerant Computing Symposium, Tokyo, Japan, pp. 234-239 (June 1988).

- 3. Y. Tamir, M. Tremblay, and D. A. Rennels, "The Implementation and Application of Micro Rollbacks in Fault-Tolerant VLSI Systems," Computer Science Department Technical Report CSD-880004, University of California, Los Angeles, CA (January 1988).

- 4. Y. Tamir, M. Liang, T. Lai, and M. Tremblay, "The UCLA Mirror Processor: A Building Block for Self-Checking Self-Repairing Computing Nodes," 21st Fault-Tolerant Computing Symposium, Montreal, Canada (June 1991).

- 5. Y. Tamir, M. Liang, T. Lai, and M. Tremblay, "The UCLA Mirror Processor: A Building Block for Self-Checking Self-Repairing Computing Nodes," Computer Science Department Technical Report CSD-900040, University of California, Los Angeles, CA (November 1990).

- 6. M. Tremblay and Y. Tamir, "Fault-Tolerance for High-Performance Multi-Module VLSI Systems Using Micro Rollback," *Decennial Caltech Conference on VLSI*, Pasadena, CA (March 1989).

- 7. M. Tremblay and Y. Tamir, "Support for Fault Tolerance in VLSI Processors," *International Symposium on Circuits and Systems*, Portland, OR (May 1989).

- 8. M. Tremblay and T. Lang, "VLSI Implementation of a Shift-Register File," Proceedings of the 20th Hawaii International Conference on System Sciences, pp. 112-121 (January 1987).

- 9. M. Tremblay and Y. Tamir, "Fault-Tolerance for High-Performance Multi-Module VLSI Systems Using Micro Rollback," Computer Science Department Technical Report CSD-880099, University of California, Los Angeles, CA (December 1988).

- 10. M. Tremblay and Y. Tamir, "Support for Fault Tolerance in VLSI Processors," Computer Science Department Technical Report CSD-890009, University of California, Los Angeles, CA (January 1989).

#### ABSTRACT OF THE DISSERTATION

High-Performance Fault-Tolerant VLSI Systems

Using Micro Rollback

by

Marc Tremblay

Doctor of Philosophy in Computer Science University of California, Los Angeles, 1991 Professor Yuval Tamir, Chair

This dissertation addresses the problem of achieving both a high level of fault tolerance and high performance in VLSI computer systems. New implementation techniques are proposed for systems operating in hostile environments where a high rate of errors is expected. Due to the real-time constraints commonly imposed on such systems, long interruptions of service are not acceptable. Hence, both error detection and error recovery must be rapid and robust.

Checkers and encoders on the critical path for intermodule communication are a major cause of performance degradation in many fault-tolerant systems. This performance degradation can be eliminated if error detection is allowed to proceed in parallel rather than in series with intermodule communication.

The fundamental new technique proposed in this thesis, micro rollback, allows the use of extensive error detection mechanisms without compromising system performance. Error detection is performed in parallel with normal execution. If errors are detected, micro rollback restores modules to a previous error-free state. Micro rollback is based on the optimistic assumption that system

components are fault free *most of the time*. This allows modules to be optimized for the normal case when no errors occurs.

Efficient techniques for adding micro rollback to a processor and other modules are described. VLSI layouts and extensive simulations of key building blocks demonstrate that the proposed techniques involve small area overheads and minimal performance degradation.

In a multi-module system, rollback to a consistent global state requires coordination among the modules. We introduce a novel hardware mechanism for logging the occurrence of recent intermodule transactions. During a rollback, these logs are used to compute the appropriate rollback distance for each module. Through the design of specific rollback domain interface units, we also show that standard modules not capable of rollback can interact with modules belonging to the rollback domain.

The integration of micro rollback with speedup techniques for uniprocessors, such as out-of-order execution and register renaming, shows that a high level of fault tolerance can be achieved for high-performance processors.

# Chapter One

## Introduction

The widespread use of VLSI digital systems running critical applications in "hostile" environments, has resulted in the development of systems able to operate reliably in the presence of isolated faults. The reliability requirements for systems operating in harsh environments, such as air-borne or space-borne computers, demand that only momentary cessation of processing be tolerated. Since most errors are caused by transient failures [Cast82], the ability to detect and recover quickly from transient faults is directly related to the reliability of a computer system. Systems capable of operating *reliably* despite the occurrence of errors, are said to be *fault-tolerant*.

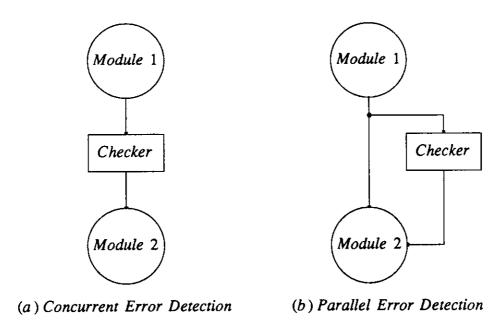

One of the keys to achieving a high degree of fault tolerance is the ability to detect errors immediately after they occur and prevent erroneous information from spreading throughout the system. Traditionally this had been achieved through concurrent error detection, which is designed to detect the first error resulting from a fault in the system. To achieve concurrent error detection and confine the damage caused by the error to the failed module, it is often necessary to check the outputs of the module continuously (during every clock cycle for synchronous systems). These requirements are usually satisfied by connecting checkers and isolation circuits in the communication path between each module and the rest of the system (Figure 1.1(a)). Consequently, concurrent error detection results in longer clock cycle times in order to allow the checks to complete. Alternatively, checking delays can be pipelined, resulting in additional pipeline stages thus

diminishing throughput whenever the pipeline needs to be flushed or is not full due to data dependencies. Hence, systems with high-coverage concurrent error detection often experience significant performance penalties due to checking delays. Moreover, these delays can compound as, for example, when a processor reads a memory word, and (1) Hamming Code checks are made, (2) the word is encoded for bus transmission, and (3) the word is checked when it arrives at the processor before use.

Figure 1.1: Concurrent error detection vs. parallel error detection.

One way to solve the problem described above is to perform checking in parallel with the transmission of information between modules (Figure 1.1(b)). The receiving module does not wait for checks to complete. It proceeds with execution as the check is being carried out and the checking result is sent one (or a few) cycles later.

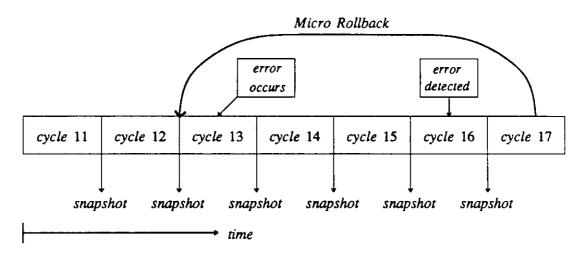

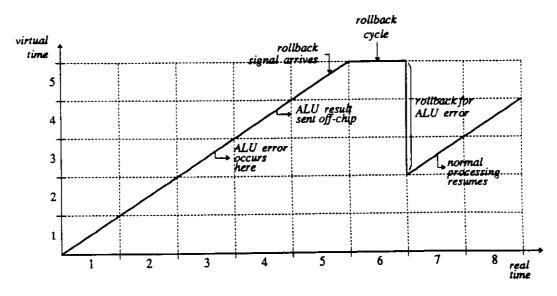

Performing error checking in parallel with inter-module communication

largely solves the problem of checking delays, but it introduces a new problem in recovery. The state of the system (starting with the receiving module) may be polluted with damaged information before an error signal arrives. Therefore it is necessary to back up processing to the state that existed just before the error first occurred. This returns the system to an error-free state where the offending operation can be retried (or correction may be attempted by other means such as restoring information from a redundant module or initiating higher level rollback). We call the process of backing up a system several cycles in response to an error signal, *micro rollback* [Tami88b, Tami90].

This dissertation addresses the problem of achieving a high level of fault tolerance in computer systems while maintaining high performance. With *micro rollback*, parallel error detection can be used, thus removing error detection circuits from critical paths. General techniques for efficient implementation of micro rollback in processors and other modules are described throughout the thesis. It is shown that micro rollback can be integrated with many speedup techniques, thus demonstrating that micro rollback can serve as a basis for high-performance, highly reliable computer systems.

#### 1.1. Applications of Micro Rollback

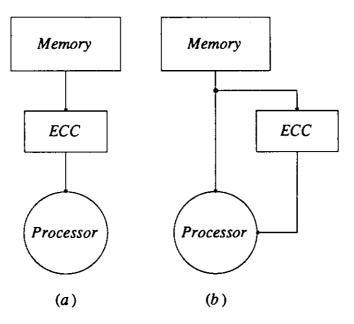

Systems using concurrent error detection can benefit from micro rollback by replacing the error detection mechanism with a parallel scheme. For example, if data in a cache memory is stored along with check bits so that its validity can be checked upon retrieval, the logic necessary for the coding and decoding may be inserted serially between the processor and the memory (Figure 1.2(a)). The added

delay due to the error detection logic would contribute to the access time to the cache memory which is often a critical path for high performance processors [Kane87]. With micro rollback, the checkers (or correction circuitry) can be removed from this critical path. The error detection can occur in parallel (Figure 1.2(b)) and the error signal can be sent after the data has arrived.

Figure 1.2: Application of parallel error detection for a processor-memory system

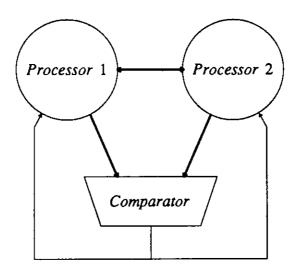

Another important use of parallel checks is in duplex systems [Down64] where error detection is accomplished by running two identical subsystems in parallel and comparing their outputs (Figure 1.3). With this technique, which is supported by some current commercial chips [AMD87], the two subsystems may be on different chips and there is thus a significant delay in getting both outputs to the comparator (off chip communication) and obtaining the results of the comparison. With micro rollback, the processors do not have to wait for the output

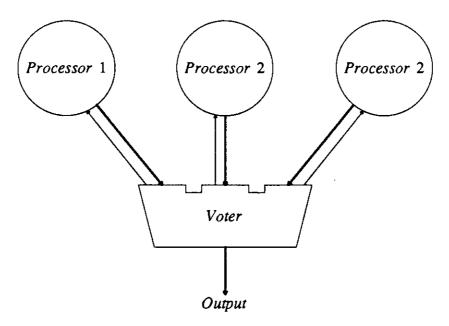

of the comparator to resume operation — upon a mismatch both processors are forced to roll back to a point in time where they were both in agreement. A system based on triplication and voting (TMR) can benefit from micro rollback in a similar way (Figure 1.4). During normal execution, the three modules execute instructions without waiting for the outcome of the voting. When voting indicates a disagreement, the modules are brought back to an error-free state using micro rollback.

Figure 1.3: Processors operating in duplex mode

Duplex mode operation and TMR both use redundancy in space. Micro rollback can also be used for systems in which checking is done using time redundancy. With time redundancy, the same hardware is used to compute logic or arithmetic operations that can confirm the validity of the results. The operation performed by the hardware to validate the results, can be the same — in which case a simple comparison between the two results is sufficient, or different — in which case a "match" is established through a relation between the two results. For

Figure 1.4: Processors running in Triple Modular Redundancy (TMR).

instance a combined multiplier/divider functional unit can be used to validate a multiplication through a division.

Time redundancy can be achieved at small cost (small hardware overhead) by using alternating logic [Reyn78]. Circuits such as adders and multipliers can be slightly modified so that when fed with complemented operands they produce a result which is the complement of the one obtained with non-complemented operands. Recomputing with Shifted Operands (RESO [Pate82]) is another method for using redundancy in time — the second computation is done using shifted operands (shifted left), producing a result which is then shifted right in order to compare it with the original result. In a fault-free circuit, the second computation matches the original result (Figure 1.5). Although savings in area are achieved through time redundancy, the main drawback of this method is the added delay required to recompute the result and compare the two values. Using micro

Figure 1.5: Error detection by Recomputing with Shifted Operands (RESO). The first result is computed with the original operands and stored into the register (using first set of control signals). The second result is calculated using shifted operands (shifted left k positions). The second result is shifted right by k positions and compared with the original result.

rollback, the second result can be computed in parallel with normal execution. If an error is detected, the processor is rolled back to a point before the computation error occurred.

In a multi-module system, a high level of fault tolerance can be achieved by making each module self-checking (Figure 1.6). When an error is detected by one of the modules, it is reported to the rest of the system C cycles later where C

represents the error detection latency. A recovery procedure such as software rollback can then be initiated so that process can resume within a few milliseconds. Although quite useful in many situations (e.g. general purpose computing), the method described above cannot be used in a context of real time control or in an environment subject to a high rate of faults.

Figure 1.6: System with Self-Checking Modules

In tightly-coupled multi-module systems, micro rollback can be used to provide faster error recovery than software-based techniques. Upon detecting an error, a module sends a rollback signal to the other modules in the system, thereby requesting a rollback to a global fault-free state. Using records of previous intermodule interactions, all the modules must then coordinate their individual rollbacks, to achieve a consistent, error-free, system state. After all the modules have rolled back (in parallel), normal system operation can resume.

#### 1.2. Implementation of Micro Rollback

The previous examples have shown how micro rollback, once combined with some error detection mechanisms, can reduce or even eliminate overheads encountered in traditional fault tolerant systems. This, as we will see in the next chapters, is possible only if micro rollback can be implemented efficiently without adding significant delay. A straightforward implementation of micro rollback could lead to a significant increase in area and could introduce delays by attaching circuitry to critical paths.

Throughout this work we present novel architectures that exploit micro rollback capabilities for achieving a high degree of reliability but also try to minimize the overhead on the system. While presenting these new ideas and exposing their benefits, we also *implement* (detailed layouts, logic simulations, extensive SPICE simulations, etc) the designs in order to know in details the impact of our ideas on the system. Bearing in mind that fabrication of the modules would lead to better absolute measurements, we compare our delays and area metrics to other modules implemented using the same technology, and when possible laid out by the same designer. This work has led to the development of a complete processor through class projects [Trem88] and other efforts [Tami91].

# 1.3. Organization of this Work

In Chapter 2 we provide a brief overview of common error detection and correction techniques for computer systems. We also examine hardware mechanisms for reversing recent state changes in processors. These mechanisms are directly related to micro rollback even though they were originally developed

for supporting precise interrupts and efficient handling of mis-predicted conditional branches.

An additional benefit of using micro rollback is the possibility of using "cheaper" checkers (in terms of area) for error detection. Since long error detection latencies have little impact on performance, it is possible to use slow checkers, which are small and simple. If error detection is on the critical path for performance, it is necessary to use fast checkers, which may be large and complex. In Chapter 3 we describe and evaluate the VLSI implementations of checkers that are commonly used for error detection and correction.

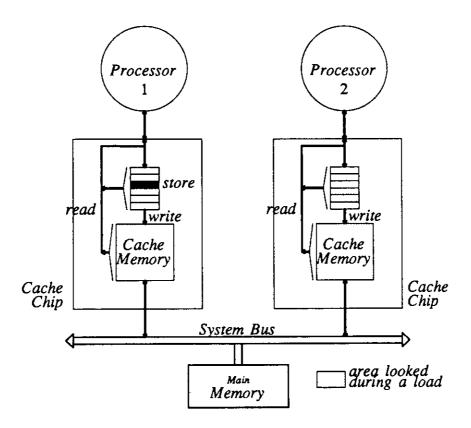

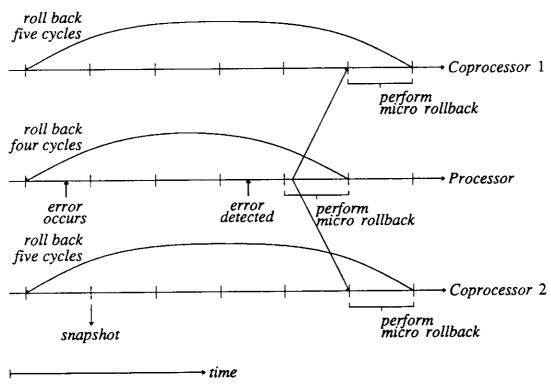

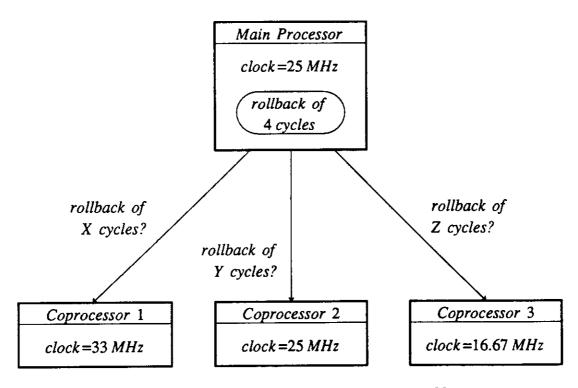

We present in Chapter 4, techniques for an *efficient* implementation of micro rollback in VLSI systems. We focus on building blocks for a VLSI RISC processor that is capable of micro rollback. We show how the updated state of the entire processor can be checkpointed after every cycle without replicating all the storage. Based on VLSI layout and circuit simulation of key modules, it is shown that the micro rollback functionality can be added with only a small performance penalty and with a low area penalty relative to the size of the entire chip. We will also discuss the implementation of a cache capable of micro rollback as well as the problems (with their solution) encountered in a multi-processor environment with shared memory.

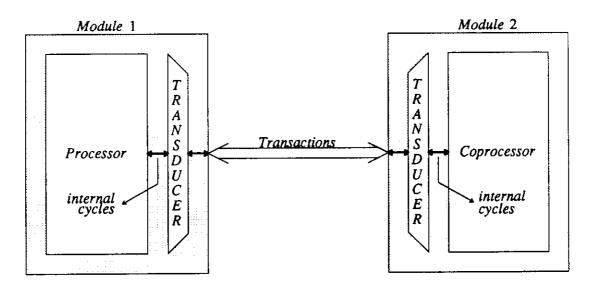

The implementation of micro rollback in a multi-module system is discussed in Chapter 5. Asynchronous and synchronous systems are both covered. Transducer modules performing translation between a number of cycles to rollback and a number of transactions to rollback (and vice-versa), are introduced in this chapter. Those relatively small modules are implemented through full pass gate

logic and perform the mapping without interfering with the basic number of cycles required to rollback.

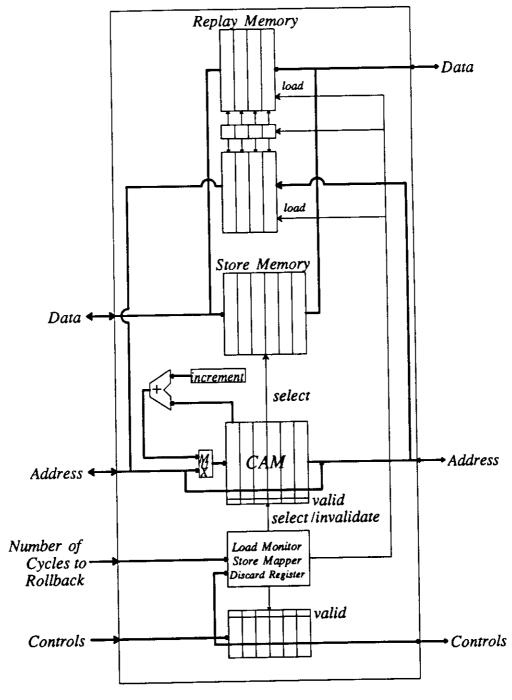

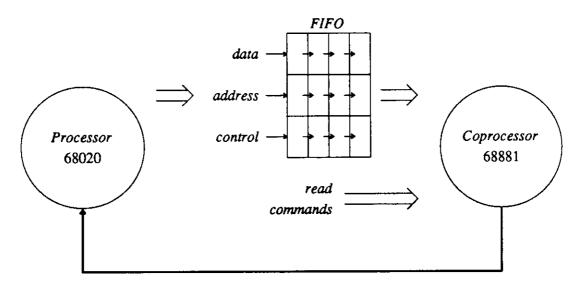

Chapter 6 describes the problem of interfacing off-the-shelves modules with modules capable of rollback. It is shown that modules that can roll back and modules that are not capable of rollback cannot communicate directly and must exchange information through a rollback domain interface unit (RDIU). The purpose of the RDIU is to delay (buffer) all transfers to modules which are incapable of rollback and whose state might be corrupted if these transfers are erroneous. Transfers from modules which are incapable of rollback are recorded in a replay memory so that they can be retransmitted to modules inside the rollback domain following a rollback. We describe several off-the-shelf memory systems that can be part of a rollback system by connecting them to the system through a RDIU. We address the issue of integrating a processor capable of micro rollback with standard loosely-coupled and tightly-coupled coprocessors.

The combination of micro rollback and techniques used to increase the performance of uniprocessors is discussed in Chapter 7. Techniques such as out-of-order execution of instructions, branch repair, and register renaming are combined in a single structure (called a standby reorder buffer) which also provides micro rollback. Sharing of the circuitry for the techniques mentioned above, leads to a low area overhead.

# Chapter Two

# **Previous Work**

The development of fault tolerance techniques has improved the ability of computer systems to cope with hardware component failures. This has led to the development of highly reliable computer systems, such as the STAR [Aviz71a, Aviz72], FTMP [Hopk78], SIFT [Wens78], Tandem [Mack78], and Stratus [Wils85]. Several error detection methods often found in those computer systems are summarized in this chapter. A micro program control unit with extensive concurrent error detection is described in details in Section 2.2. Forward and backward recovery methods are described in Section 2.3. Specifically, we discuss *instruction retry* as an example of a backward recovery method. Rollback techniques used for supporting precise interrupts and handling of mispredicted conditional branches are covered in Section 2.3.

#### 2.1. Error Detection

The first step in fault-tolerance is to detect errors occurring in the system. The purpose of error detection is to prevent system failures by recognizing that they may be about to happen and initiate corrective actions.

Possible errors in VLSI chips include: corruption of the contents of storage elements, incorrect results produced by computation modules (e.g., an ALU), and corruption of data and control signals (e.g., buses). These errors are the result of transient or permanent faults due to design and fabrication flaws (e.g., marginal timing, incorrect dosage of ion implants), environmental factors (e.g., noise,

radiation), and wear-out mechanisms (e.g., electromigration) [Doyl81]. Since micro rollback is aimed at removing delays introduced by checkers it is important to understand how error detection is performed and what are the different methods used. The VLSI implementation of some of these methods is described in Chapter 3. Among several error detection methods, we mention:

Parity: a bit representing the XOR of every data bits in a word is sufficient to detect all single bit errors as well as all odd-weight errors [Hamm50]. This technique is used in many systems, either to detect errors in storage elements, or to detect errors after transmission through a bus [Kane87].

Codes for memories: several types of codes have been applied successfully to memory systems. Most of the codes fall can be categorized into two families [Rao89]; linear codes, which are usually derivatives of Hamming Code [Hamm50], and cyclic codes such as linear feedback shift register (LFSR) [Froh77]. The principle behind these codes is simple. Words are encoded prior to transmission or storage, and they are checked upon reception or retrieval. Besides detecting errors, most of the codes offer the possibility (with larger overhead) to correct a number of errors.

Arithmetic error codes: this family of codes is useful for the design of computational unit since they serve to detect errors in the results produced by arithmetic processors as well as the errors which have been caused by faulty transmission or storage [Aviz71b].

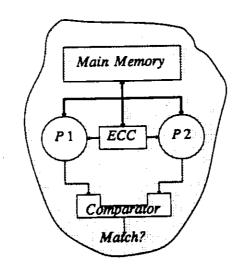

Duplex mode operation: errors observable at the boundary of a module can be detected by running two identical modules in lockstep and having their outputs feed a comparator [Down64, John84, AMD87].

Alternating logic: this technique achieves its fault detection capability by utilizing redundancy in time instead of the conventional space redundancy and is based on the successive execution of a required function and its dual [Reyn78]. Logic designs of binary adders and multipliers using alternating logic have been described in [Take80].

Self-exercising self-checking modules: to prevent accumulation of dormant faults, modules can be made self-exercising [Renn86]. Additional logic is added to the basic circuitry of a module in order to periodically activate and test all parts of the module. This logic can be combined with a simple recovery mechanism (e.g. Hamming code) to allow rapid recovery before multiple errors build up. Memory designs making use of this technique have been proposed in [Renn86] and the methodology has been extended to the design of a complete processor in [Chau88].

# 2.2. Micro Program Control Unit with Concurrent Error Detection

The techniques mentioned above can be used individually or they can be combined in order to enhance the level of fault tolerance that a system can reach. As an example, we look at the VLSI implementation of a microprogram control unit with concurrent error detection [Yen87]. The paper describes several techniques used in order to make the unit self-checking. Specifically, the

## techniques used are:

- coding techniques for detecting unidirectional errors

- dual-rail codes for a few control signals

- duplication for some of the submodules

- layout-based code-word checkers

- the PLA is strongly fault secure and strongly code disjoint

- the PLA is implemented using a modified Berger Code [Mak82]

The addition of these techniques to a basic control unit (in this case, an Am2910 look-alike) is costly in terms of area, and impairs performance because of additional delays required to compute codes and because of added capacitance on various parts of the circuitry. The Concurrent Error Detection (CED) method is then compared with a simpler method consisting of a duplication of the complete functional modules (duplex mode) [Down64, John84, AMD87]. The conclusions extracted from this article (in quotes) and our own remarks are:

- (1) "The duplex method is easier to design".

- (2) "The duplex method has extensive fault coverage for faults in one of the duplicated modules".

- (3) The authors estimate that "the duplex mode method would take 138% more area than a simple Micro Control Unit (MCU) which represents 20% more area than the Concurrent Error Detection (CED) method". This calculation based on an estimate of the area taken by check bits generators. In [Trem89a] we discuss the implementation of data compression circuits and we believe that the area overhead could be reduced significantly compared to the estimates in [Yen87]. Specifically,

we believe that efficient compression and comparison circuits combined with the duplication of the modules should lead to a more reasonable overhead of 110% (compared to 138%).

- (4) "The duplex method has slightly less performance". The extra logic needed for the CED method is part of the control circuitry and is thus bound to affect the timing of critical paths on the chips, resulting in decreased performance. With the duplex method, the basic chip is kept intact so that the performance of the basic processor is not degraded. However, if the processors must wait for the outcome of the comparison at the end of every cycle, performance can be significantly reduced. If there is no need to wait for the output of the comparison, the performance degradation can be eliminated. This is possible if either there is no need to support fast local recovery or micro rollback is used. In the first case, after an error occurs, the processors will continue to operate, with erroneous data, until the mismatch signal triggers system-level recovery. This recovery can then restore the processors to a state that was saved (checkpointed) many cycles prior to the occurrence of the error [Rand78]. In the latter case, as described in Section 1.1, micro rollback is used to "hide" the error detection latency. Once a mismatch is detected, the processors are quickly rolled back a few cycles, to their state just prior to the occurrence of the error.

- (5) "The CED method is able to perform fault diagnosis with greater resolution". This is important for error recovery. If a low latency recovery is desired, a combination of the two methods can be performed as we shall see in Chapter 4.

The conclusions drawn from the article and our own observations indicate that the duplex method is more viable than the CED method, based on overhead in terms of area, performance, and ease of design.

#### 2.3. Error Recovery

Once an error is detected by hardware checkers, actions must be taken to "repair" the damage caused by the fault and resume program execution. Two techniques described in [Rand78], called *forward error recovery* and *backward error recovery*, attempt to place the system in a *valid* state from which processing can resume. After describing these two techniques, a backward error recovery method related to micro rollback, namely *instruction retry*, is discussed.

# 2.3.1. Forward Error Recovery

Forward error recovery schemes attempt to make use of the erroneous system state, to make further progress. For example, in several operating systems, recovery procedures following a crash are based on the state of the system at crash time. Some jobs not affected by the crash will be able to proceed while other jobs, which were executing in main memory, may not be able to resume. Because correct identification of the error is often necessary to allow continuation of the process, forward error recovery schemes are designed as integral parts of the system they serve [Rand78]. An example of a detection of an error in a TMR system (Figure 2.1), and a subsequent recovery through forward error recovery, is shown in Figure 2.2.

At a lower level we can consider the use of Error Correcting Codes (ECC) for various systems such as the Cray X-MP, as a forward error recovery strategy. The detection of a bit error in a memory word is accomplished through separated

Figure 2.1: Triple modular redundancy with triplicate voters.

Figure 2.2: Forward error recovery through a "roll forward".

dedicated hardware which, upon the detection of an error, gives a *state* from which the correction circuitry can flip the specific bit so that process can go on [Cray84]. The circuitry for both error detection and error correction is connected serially with accesses to memory. Thus, even in case of an error correction, the process is not interrupted. However, delay is added to each memory access. In the case of the Cray X-MP, serial ECC takes 0.5 processor cycle (the latency of a memory access is 14 processor cycles) [Cray84].

Davis in [Davi85] describes the use of ECC for a high density CMOS memory chip, using the same principles discussed above. In his paper Davis mentions that the forward recovery scheme using ECC does not add any delay to the memory access time. This is only true because during a word access (16 bits), one of the two data bytes is delayed for 15ns by an RC chain to avoid excessive power-supply noise. During that extra delay of 15ns the ECC circuitry can correct any one-bit error, an operation taking 10ns, without adding extra delay. On the other hand, for a chip operating at its full potential, i.e. when both bytes are presented at the same time, the ECC delay would be added to the critical path, making the chip significantly slower.

#### 2.3.2. Backward Error Recovery

Backward error recovery relies on the periodic saving of the *state* of the system, an action called checkpointing [Rand78]. The *recovery points* thus created, represent error-free states from which the system can resume execution. The action of bringing a process back to an error-free state is called *rollback*.

If errors do not occur often and if long recovery procedures and loss of work

during recovery are acceptable, software methods can be used. Thus, checkpointing may be performed only once every few millions (or billions) of cycles and recovery may be software controlled so that the recovery process itself may take many thousands of cycles [Koo87].

In our research we are more concerned with systems designed for environments where error rates are high and/or real-time constraints prohibit significant delays for recovery. As we shall explain later, our work provides hardware-supported checkpointing and rollback.

Figure 2.3: Checkpointing and recovery through rollback.

The backward error recovery concept can be used to "hide" the time to perform error detection and correction. Based on the assumption that errors do not occur often, it is wise to take any extra delay out of the critical path for a certain module or out of the communication path between two modules. If a module can checkpoint periodically, then error detection for actions occurring after a checkpoint can have a relatively long latency since the *state* of the module can always be brought back to the recovery point (Figure 2.3).

If there is enough time between two successive states to perform error detection and/or correction (plus a certain margin), rollback simply consists of aborting the execution of the current operation before an erroneous modification of the state occurs (Figure 2.4). In this case, the checkpoint is the state reached before the operation started, which is the current state since the operation was aborted before any damage occurred. The Memory Management Unit (MMU) of the IBM ROMP processor used the latter feature to take error correction out of the critical path for each access request by the processor to the MMU [Wald85]. The two-cycle memory access time required for the chip set includes: address translation, address and data buffering, and ECC error detection. Error correction time is not included in the access time, if an error is detected, the data sent to the processor is "intercepted" and the corrected data is then resent on a subsequent cycle. According to [Wald85] this practice reduced the impact of ECC on access time from 80ns to about 30ns.

Figure 2.4: A short error detection latency allows cancellation of an instruction.

#### 2.3.3. Instruction Retry

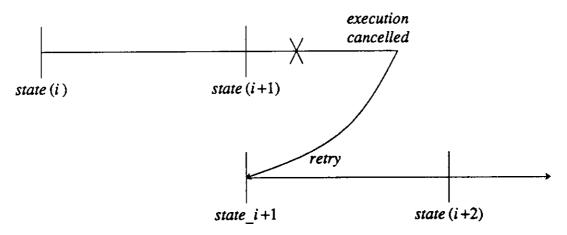

For systems in which the latency of the error detection mechanisms is too long for a simple cycle cancellation, a method called "instruction retry" can be used.

With the instruction retry method, the state of the processor is checkpointed at each instruction boundary. Then, upon the detection of an error during the execution of instruction 'j', the state present after instruction 'j-1' is restored, and execution resumes. In this way the error detection latency is stretched from one machine cycle to the instruction latency of the fastest instruction (smallest latency). But because of the various instruction latencies present in the instruction set of a processor, the storage for checkpointing each instruction must be based on the longest instruction or on the instruction which changes the most states. For example, if a processor executes instructions with latencies varying from 2 cycles to 8 cycles, the error detection latency must be smaller than 2 and the storage must be large enough to accommodate up to 8 changes of state. The controls for such a "temporary storage" become quite complex when a wide range of instruction latency is present in the instruction set of a processor.

The IBM 4341 processor uses instruction retry to recover from errors detected by the three following error detection methods: [Ciac81]

- duplication and comparison of the lines

- parity bit

- detection of special error conditions (e.g. invalid control register)

When a malfunction is detected, either the operation is successfully retried or

that is continuously saved and periodically purged by hardware. If the instruction needs to be aborted, information regarding the cause of the termination is sent to the *machine check interrupt process*. Ciacelli claims that the saving and purging does not affect the performance of the machine. For a VLSI processor we anticipate that instruction retry would impair performance slightly. Based on our experience [Tami91] we believe that the insertion of *shadow registers* for saving the processor state as well as the extra control signals needed for the retry mechanism would lead to increased bus capacitance and more complex controls, which both contribute to lower performance.

An implementation of error detection and *instruction retry* for a VLSI microprocessor is described in [Tsao82]. The error detection techniques implemented are:

- a self-checking PLA for the control part,

- parity checkers for the buses,

ALU errors are not detected unless the chip is matched with an identical chip running in master-slave configuration (duplex mode). The authors acknowledge that the error detection hardware is limited (due to area consideration) but they claim that if the chip is used in a master-slave configuration, single transient errors are all detected.

In [Tsao82], upon the detection of an error occurring during the execution of the current instruction, the processor has to capability to retry that same instruction. To accomplish this, a shadow register is attached to every single state register on the chip. The shadow registers hold the contents of the state registers

which were present at the end of the previous instruction. If an error is detected, the modifications made to the state registers during the execution of the current instruction are discarded and the previous contents are restored from the shadow registers.

The method described is efficient for simple error detection mechanisms and for simple processors, such as the Fairchild F8 used as the target machine, but is not viable for more sophisticated error detection techniques combined with modern VLSI pipelined processors. Using the proposed instruction retry method, the detection of the error must occur before the execution of the following instruction (or when the *normal* state register is copied to the shadow register). In this case the detection must either (a) be executed serially with the execution of each instruction — a severe loss in performance, or (b) be executed in parallel — a severe time restriction limiting the complexity of the of the detection technique that can be used.

For modern processors, there are several other problems with instruction retry. First, the state of modern VLSI processor is large and precludes the use of shadow registers for every single register (the register file for example would have to be duplicated, adding from 32 to 128 extra registers to the layout). Secondly, modern RISC processors are heavily pipelined to increase performance. This has the effect of having several instructions executing in parallel in different stages of the pipeline. To "retry" a single instruction becomes more complicated due to the following reasons:

(1) Different instructions take different number of cycles to execute. The instruction retry mechanism would have to be designed to accommodate several

"kinds" of instructions.

(2) Modern processors achieve high performance by supporting out-of-order execution of instructions. By definition, instruction retry requires the processor to roll back to a precise instruction boundary [Smit88]. The ability to roll back to a precise instruction boundary is also needed in order to support the normal semantics of interrupts and exceptions [Smit88]. Since instructions modify processor state out-of-order with respect to the order in which they are issued, complex dedicated hardware is required in order to support precise exceptions [Smit88, Hwu87]. The overheads associated with this hardware are significant, leading to many recent processor designs which avoid full support for precise exceptions [Sun91, Groh90]. Identical hardware is required to support instruction retry. Hence, instruction retry mandates the overheads associated with support for rollback to precise instruction boundaries. Micro rollback, on the other hand, can be implemented for these processors at a significantly lower cost (Section 4.2).

We will describe, in Chapter 3, error detection methods that offer high coverage at the expense of long error detection latencies (beyond a single instruction). We will also describe, in Chapter 5, multi-modules systems where errors signals are propagated throughout the system without having any knowledge of what kind of instructions different modules are executing. With instruction retry, it would be very difficult to synchronize the error signal with the execution of a particular instruction. The results from Chapter 3, Chapter 4 and Chapter 5, will show that it is desirable to have a repair mechanism that offers:

(1) Independence between processor performance and the error detection latency.

This allows the use of error detection mechanisms with long latencies without decreasing the processor performance.

- (2) Independence between the retry mechanism and the instruction semantics of the module (in order to simplify the implementation)

- (3) Independence between different modules. Modules do not need to know the specific instructions that other modules are executing. The synchronization of the retry mechanism should be simple and based on semantics-free synchronization points (e.g. cycles).

The technique that we propose, micro rollback, offers the advantages described above. It differs from instruction retry since rollback is performed on the basis of *clock cycles* rather than instructions. This allows rollback to be executed at the logic level, without keeping track of instruction semantics and instruction pipeline conditions. As a result, the micro rollback capability can be *independently* implemented in each module of a synchronous system, regardless of its function, by following very simple specifications — it must be possible to roll back all storage elements by any number of cycles up to a specified limit (Chapter 4). Building blocks which are capable of micro rollback can be interconnected in arbitrary ways to construct synchronous *systems* capable of micro rollback (chapter 5). Such flexibility is difficult to achieve if the semantics of rollback are tightly coupled to the specific function of each module.

#### 2.4. Related Work

## Comparison with precise interrupts methods

At the micro-architecture level, the technique we present for micro rollback of the register file has some similarities with schemes for precise interrupts in high-performance processors [Smit88, Hwu87]. Because high-performance processors are heavily pipelined, so that several instructions can executed simultaneously, and because of the different latencies of the processor's functional units, instructions are often allowed to modify the state of the processor in a different order from which they were issued.

During the execution of a program, if an interrupt occurs, the state of the running processor may not reflect the state that the processor would have if the instructions were executed sequentially. This occurs when instructions modify the processor state out-of-order. For example, an integer addition (short latency) issued after a floating-point divide (long latency) may complete and send its result to the register file before the divide completes. If the divide instruction later causes an exception (e.g. divide by zero, overflow, etc.), the current processor state does not represent the state present when the divide was issued. In order to resume operation quickly after an exception, it is essential to have access to the state present before the instruction causing the exception was issued. Special techniques have been proposed [Smit88, Hwu87, Mele89] to "recover" the proper state so that execution can proceed upon termination of the interrupt.

An analogy can be drawn between *repairing* the state of a processor in order to process an interrupt, and *repairing* the state of a module following the detection

of an error. In both cases we have to undo portions of instructions that should not have been executed. In the context of out-of-order execution machines, higher performance is achieved by issuing instructions speculatively hoping that previously issued instructions will not cause an exception. In the context of fault tolerance, modules proceed conditionally hoping that the error detection mechanisms will not signal that an error has occurred a few cycles ago. In both cases special techniques must be provided so that the state of the processor/module can be repaired for execution to resume. We will give in Chapter 4 a more extensive comparison between the different techniques. Specifically we will compare the Delayed-Write Buffer (DWB) with a reorder buffer with bypasses [Smit88] and with the forward difference scheme [Hwu87]. We will show that micro rollback is inherently simpler — there is no need to keep track of instruction boundaries since the rollback event is transparent to the software. Also many of the proposed schemes for precise interrupts will be shown to require multi-cycle rollback, increased bandwidth to storage elements, and complex control.

# Exception repair mechanism for the Motorola 88000

A high performance VLSI RISC processor, such as the Motorola 88100, in which several *Special Function Units* (SFU) can operate in parallel, requires special hardware to be able to handle exceptions. The processor's SFUs have different pipeline latencies and exceptions can occur at various stages of the pipeline. Because of the complexity of building an *exception repair mechanism*, Motorola chose a combination of hardware components and software routines to

handle exceptions.

The processor contains several "shadow" registers which are copies of the register they accompany. For example, each one of the Execute, Next and Fetch instruction (pointers to instructions) have a shadow register. Upon the detection of an external interrupt or an internal exception, the shadow-freeze (Sfrz) bit of the processor-status register (PSR) is set and all the shadow registers freeze. All SFUs also freeze and the instruction unit fetches the instruction pointed to by an exception vector.

Handling of a trap instruction is slightly different. The machine "synchronizes" itself before taking the trap. The SFUs are emptied, memory accesses are completed, and the shadow registers are frozen. Trap processing then starts at the instruction pointed to by the trap vector.

The shadow register method offers the following advantages:

- it restores the processor state quickly following an exception,

- it is relatively inexpensive,

- it "frees" the normal logic for exception processing.

But it also presents the following disadvantages:

- if nested exceptions occur, the shadow registers must be saved by a software routine before jumping to the next exception (the shadow registers must also be restored upon returning from the second exception).

- it does not provide precise exception for all cases.

Imprecise exceptions occur for the Motorola 88000 because some exceptions

are reported late in the floating-point pipelines. To resume operation following an imprecise exception, several registers containing the 5-bit opcode that identifies the instruction type, the exception handler that became enabled, and the destination register for the result (plus other information), are provided. Using that information, Motorola claims that software routines can complete instructions that caused imprecise exceptions. Unfortunately using this method the processor state cannot always be restored to a correct state since the program counter cannot always be restored to the instruction following the exception-causing instruction (e.g. when a branch occurs) [Mele89]. For these cases, precise exceptions can be provided by serializing the execution of each floating-point instruction, which results in a significant reduction of performance in many applications.

# Chapter Three

# Error Detection and Correction Circuits for VLSI Processors

In many applications the performance penalty of system-wide recovery cannot be tolerated, so it is desirable for modules to include mechanisms for rapid correction of most internal errors (i.e., local recovery). In other applications, some system-level actions for recovery are acceptable but high-speed checkers are needed to detect errors as soon as they occur and prevent the spread of erroneous data throughout the system.

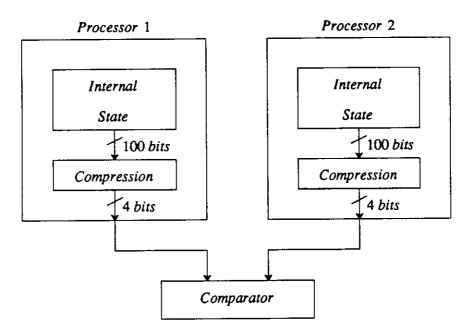

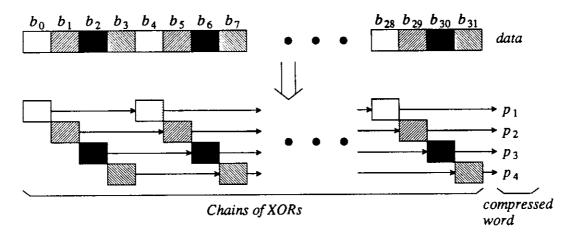

Many of the techniques used to detect and correct errors caused by hardware faults rely on a few basic components: encoders, decoders, comparators, and data compression circuitry. In a VLSI processor, coding can provide error detection and correction (EDC) for data kept in the register file and other storage (e.g. PSW, caches, TLB), as well as for data processed by the ALU (e.g. using arithmetic codes [Aviz71b]). For example, single-bit parity can detect an odd number of errors in registers, while Error Correcting Codes (ECC), such as Hamming code, provide error correction capabilities [Rao89]. Check bits must be computed every time storage is modified, and verified whenever storage is accessed. In many modern processors a modification or access of the register file can occur every cycle, thus requiring low latency and high throughput for the circuits generating and verifying check bits. To achieve higher coverage and to detect errors in other modules (not just storage), duplication and comparison can be used [Down64, Tami83] at either the module or chip level. To minimize detection latency, values

of internal nodes of modules should be compared each cycle. If most of the internal state is not observable from existing pins, numerous extra pins may be required. In order to reduce the number of extra pins, values of key internal nodes can be "compressed" efficiently (on-chip before comparison), into signatures of a few bits, with only a small reduction of coverage [Sedm80, Davi81, McCl85]. Since the comparison is done every cycle, compression and comparison must also be performed with low latency and high throughput.

The modules required to implement the error detection and correction techniques described above, consist mainly of encoders, decoders, comparators, and data compression circuits. These circuits rely extensively on Exclusive OR (XOR) gates. Alternative implementations of multi-input XOR gates are presented in Section 3.1. The different implementations are evaluated with respect to performance, area, and noise margins. The evaluation is performed in the context of the microarchitecture of a VLSI RISC processor where such modules might be used for error detection and correction.

In Section 3.2 we describe and evaluate circuits for implementing Error Correcting Codes (ECC) based on Hamming Code, in which code generation and error correction require multiple parity circuits. Through proper choice of high-speed parity circuits and the specific code to be used (M-code [Cart76, Rao89]) fast correction and check bit generation are achieved.

In Section 3.3 we discuss the comparators and data compression circuitry needed for implementing duplication and comparison. When the two modules whose outputs are being compared are on different chips, compressing the data and sending it off chip for comparison may introduce significant delays in system

operation. This potential performance penalty can be greatly reduced (as we will explain in details in subsequent chapters) by using *micro rollback* [Tami88b], which allows detection to be performed in parallel with normal system operation.

## 3.1. Implementation of Multi-Input XOR Gates

Multi-input XOR gates are key building blocks for many error detection and correction circuits. For example, a single parity bit is generated by XORing all bits in a data word. A single parity codeword is verified by XORing all bits in the codeword. Check bits in error detection and correction codes based on Hamming codes are also generated and verified by computing the parity (XOR) of a subset of the bits in the word [Rao89].

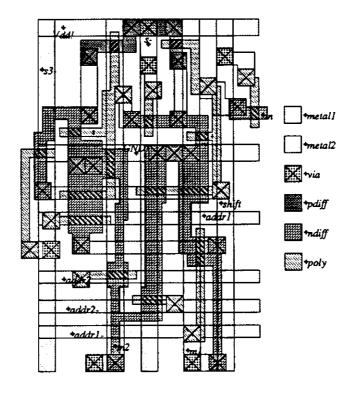

Figure 3.1: Representation of all layers for our layouts.

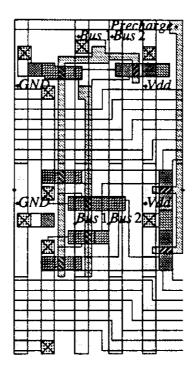

In this section we describe and evaluate several different implementations of multi-input XOR gates. Our implementation technology is double-metal  $2\,\mu$  CMOS (MOSIS SCMOS design rules with  $\lambda=1\,\mu$ ). Figure 3.1 shows how the different layers are represented throughout this thesis. The evaluation criteria are

speed, size, and noise margins. The speed is determined by circuit simulation using SPICE. The high noise margin  $(NM_H)$  is defined as the difference between the minimum high output voltage of the driving gate and the minimum input high voltage recognized by the receiving gate [West85]. The low noise margin  $(NM_L)$  is defined as the difference between the maximum low output voltage of the driving gate and the maximum input low voltage recognized by the driven gate [West85]. Our circuit simulations show that for static CMOS circuits (with  $V_{th} = 0.74 \ Volt$ ):  $NM_L = NM_H = 2.1 \ Volts$ .  $NM_L$  is kept at 2.1 Volts in all the circuits described in this chapter.  $NH_H$  varies depending on the technique used and is thus the value that we report in the discussion of the circuits.

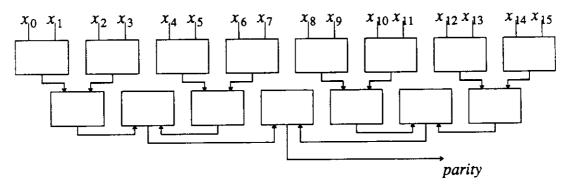

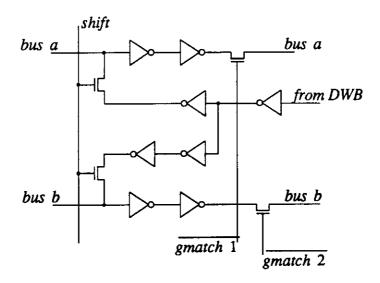

The most appropriate XOR implementation cannot be selected without considering the specific use of the circuit: where on the chip it is connected, pitch matching with other circuits, use for single bit parity or for multiple check bits in an error-correcting code, etc. As a specific example, we discuss the use of multi-input XOR gates for error detection and correction in a VLSI RISC processor. A simplified datapath of a VLSI processor is shown in Figure 3.2. Two registers can be read simultaneously from the register file and their values are transferred over internal buses to the shifter or the ALU. The internal buses are also used to transfer the results of the ALU or shift operation back to the register file [Sher84]. If the register file stores redundant bits for error detection and/or correction, values read from the register file must be sent to checkers, which verify and/or correct the data. Since two values are read simultaneously, two checkers are needed, each connected to one of the internal buses (Figure 3.2).

If the XOR gates are used for generating and checking the parity of data being

Figure 3.2: A simple processor with a two-port register file. Two bus lines are routed over the parity/ECC circuitry.

transmitted over a bus, the pitch of each cell must match the pitch of the data bus. We will first discuss the performance (delay) and size (chip area) of checkers attached to a two-port register file designed with a pitch of  $50 \lambda$ . This pitch was chosen to match the pitch of a simple processor datapath. It is the result of a compromise between two conflicting factors: (1) a smaller pitch minimizes the area of the register file, and (2) a larger pitch simplifies the layout of other datapath cells (ALU, shifter, etc) and results in a shorter datapath.

We will describe how the metrics of the parity circuits change when the data bus pitch is reduced to 39 $\lambda$ . The advantage of this pitch is that it allows a smaller implementation of the register file (numbers are given in a latter section). We will also discuss the implementation of these circuits for use with the relatively large datapath pitch (74 $\lambda$ ) of the SPUR processor [Lee89]. Given a fixed pitch, the only flexibility is with respect to the size of the cell in the direction of the bus, we henceforth called this size the *stride* of the circuit.

As shown in Figure 3.2, the internal buses are routed <u>over</u> the parity or ECC circuitry. For high performance, these internal buses are implemented in metal, typically second-level metal. The two bus lines over each cell of the parity or ECC circuitry limit the use of second-level metal in these cells, thus making the layout of the cells more difficult. The parity/ECC circuitry can reduce the performance of the datapath due to two sources of added delay: (1) the gate capacitance of the buffers which drive the parity/ECC circuit, and (2) the additional capacitance of the bus lines, which must be lengthened to accommodate the parity/ECC circuits.

Figure 3.3: 16-input tree of XORs.

# 3.1.1. Static Implementation

An M-input XOR gate can be implemented as a tree of 2-input XOR gates (Figure 3.3). The resulting stride of a tree laid out as shown in the figure is:  $(\log_2 M) \times Cell_{stride} + Metal_{line})$ . The  $Metal_{line}$  term is the stride for routing the parity signal, which is a single metal line, out of the datapath. With SCMOS

design rules,  $Metal_{line}$  is  $7\lambda$  ( $4\lambda$  for the line/contact and  $3\lambda$  for spacing). In a VLSI layout, non-rectangular modules are undesirable since it is difficult to pack them efficiently on the chip and significant chip area is wasted. However, the layout of a binary tree can be compressed to only two rows of  $\lfloor M/2 \rfloor$  cells by slightly modifying the design of the basic cell, and by reorganizing the layout as shown in of stride the becomes this the tree Figure 3.4. In case.  $2 \times Cell_{stride} + ((\lceil \log_2 M \rceil - 1) \times Metal_{line})$ . The second term is the stride required to route wires connecting XOR cells in the second row (routing wires below the cells in Figure 3.4), as well as for routing the parity signal out of the datapath. The layout of the XOR cell allows the first row to be connected to the second row without any extra stride for routing.

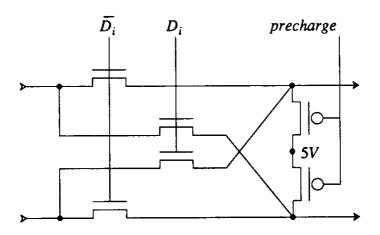

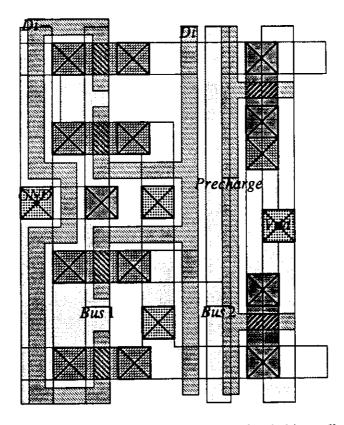

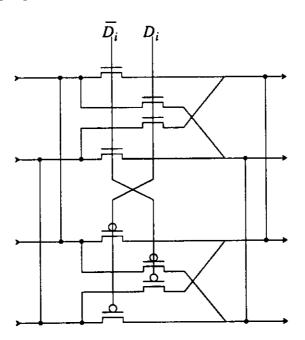

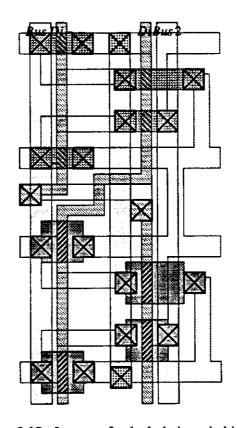

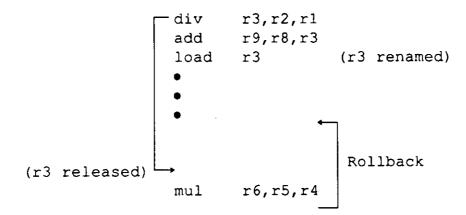

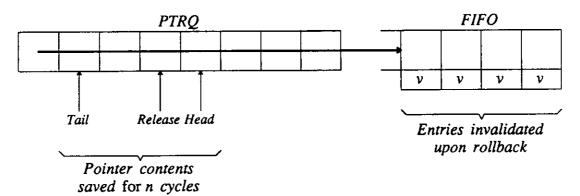

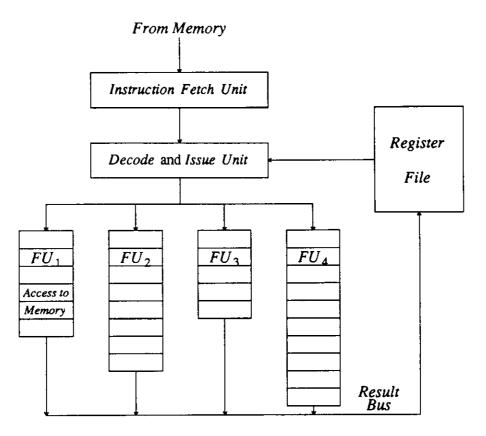

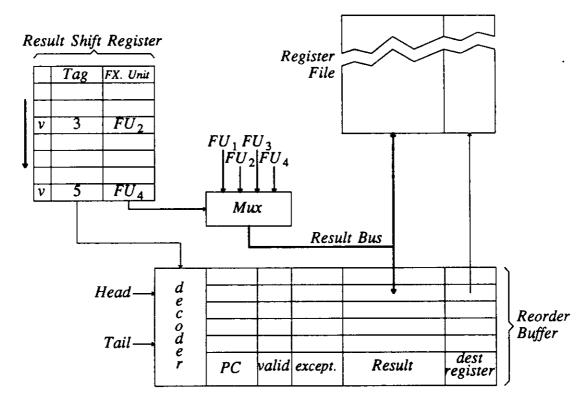

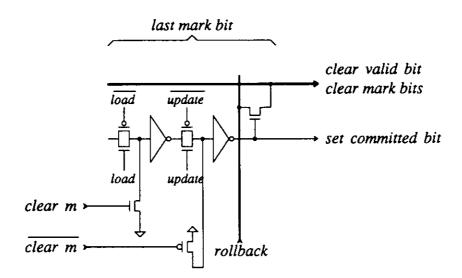

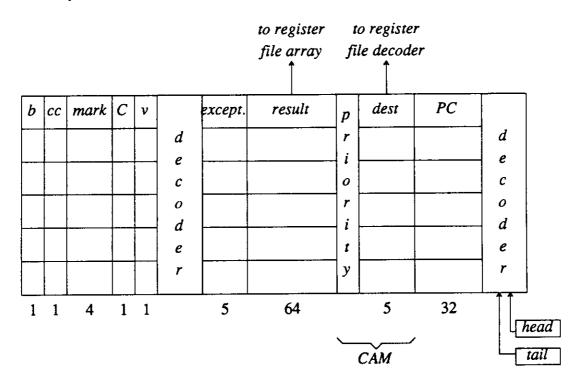

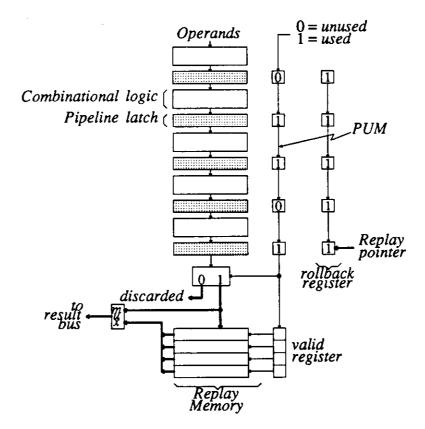

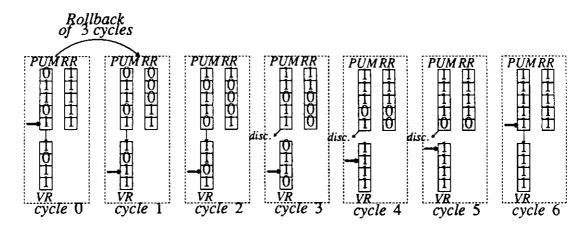

Figure 3.4: Compact layout of a 16-input tree of XORs.