#### Computer Science Department Technical Report University of California Los Angeles, CA 90024-1596

AN APPLICATIVE LANGUAGE FRAMEWORK FOR HARDWARE SYNTHESIS

**Dorab Ratan Patel**

October 1990 CSD-900031

# An Applicative Language Framework for Hardware Synthesis

Dorab Ratan Patel

September 18, 1990

#### ACKNOWLEDGMENTS

I would like to express my gratitude to my advisor, Miloš Ercegovac, for his patience, encouragement, and wisdom. Miloš is probably the best advisor anyone could ever have. He knew when to challenge me into deeper explorations and also when to leave me to explore on my own. I have learned a lot from Miloš—not only about computer science, but also about life. I would like thank Gerald Estrin for continued support throughout my graduate career, especially when I needed it the most. Jerry was always there with thoughtful advice whenever I needed him. The members of my committee: Stott Parker, Rajeev Jain and Kirby Baker deserve thanks for their comments and participation. Stott provided particularly useful feedback on appendix B.

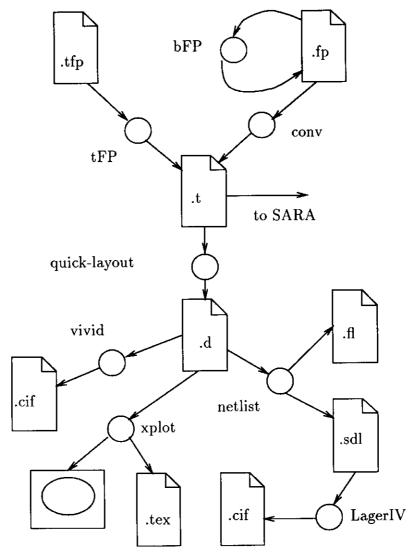

During my stay at UCLA I have had the opportunity to interact with many different students, especially in the SARA/IDEAS and FP/VLSI groups. Discussions with Martine Schlag helped clarify many of the ideas presented here. Martine also wrote the tools which were used to produce the topological layout diagrams in this dissertation. John Harding performed way beyond the call of duty helping me achieve self-sufficiency with the Lager tools.

My sojourn at UCLA was made much more comfortable by the staff of the department. In particular, I would like to thank Verra Morgan for her help easing the way through the bureaucratic labyrinth of graduate studies. Doris Sublette, of the departmental archives, was an invaluable source of information, obscure and obvious.

I have been fortunate to have friends who, by sharing the good times and bad, made the process of getting a PhD much more bearable. Beheroze Shroff and Ketu Katrak have been my friends almost since the first day I arrived in the U.S. In addition, the denizens of "Hershey Hall West" provided a congenial, supportive and neighborly environment. My "extended roommates"—Kulvant Lail, Charles Tashiro, Sarma Sastry, Neela Sastry and Christian Matthiessen—supplied companionship, food, and ... dessert. Charles also gets special mention for a thorough proof-reading of the dissertation.

Lastly, I would like to thank my parents, Mani and Ratan Patel, without whom this would not be possible. What I am today is due in large part to them.

This research was supported in part by a fellowship from Systems Engineering Laboratories, a State of California MICRO Fellowship, the Department of Energy, the Office of Naval Research, and the State of California MICRO contracts in conjunction with Systems Development Corporation, Hughes Aircraft Corporation, NCR, TRW and Rockwell International.

#### Abstract

This dissertation presents a method, based on applicative languages, for the specification, analysis, synthesis and implementation of hardware algorithms. Using the same language to represent the algorithm from specification to mask generation provides a consistent and coherent framework. Designers are provided with an environment in which they can efficiently explore alternative designs for their algorithms throughout the synthesis process. It is possible to specify the algorithm at arbitrary levels of abstraction and have the system rapidly evaluate certain parameters (e.g., speed, area) so that designers can make informed decisions during the synthesis process. Semantics-preserving transformations convert a specification to an implementation that is guaranteed to be correct. Evaluations of designs with respect to performance parameters are performed at any desired level of abstraction. A visual display of the algorithm throughout the design process provides designers with feedback on the spatial implications of their design decisions. Using an applicative language during design helps to prove the correctness of refinement and abstraction. Symbolic evaluation of the algorithm with representative symbolic inputs is used to generate a planar topological layout of the algorithm. Sequential circuits are incorporated into this applicative framework using space/time transformations. An interface to a back-end system is used to generate mask layouts from topological descriptions.

# Contents

| 1 Introduction |     |                                                                    |  |  |

|----------------|-----|--------------------------------------------------------------------|--|--|

|                | 1.1 | Complexity Management                                              |  |  |

|                |     | 1.1.1 Abstraction                                                  |  |  |

|                |     | 1.1.2 Composition                                                  |  |  |

|                |     | 1.1.3 Design Framework                                             |  |  |

|                | 1.2 | Tools                                                              |  |  |

|                | 1.3 | Exploring Alternative Designs                                      |  |  |

|                | 1.4 | Reasoning about Designs                                            |  |  |

|                | 1.5 | Specifications                                                     |  |  |

|                | 1.6 | Visual Feedback                                                    |  |  |

|                | 1.7 | Overview                                                           |  |  |

|                |     |                                                                    |  |  |

| 2              | The | $ u \mathcal{FP} $ System 24                                       |  |  |

|                | 2.1 | Brief Introduction to $\nu \mathcal{FP}$                           |  |  |

|                | 2.2 | Value and Symbolic Evaluation                                      |  |  |

|                | 2.3 | Attributes                                                         |  |  |

|                |     |                                                                    |  |  |

| 3              | App | olicative Languages in the Specification of Algorithms 32          |  |  |

|                | 3.1 | Properties of Specification Languages                              |  |  |

|                | 3.2 | Properties of Applicative Languages                                |  |  |

|                | 3.3 | Problems with Applicative Languages                                |  |  |

|                | 3.4 | Summary                                                            |  |  |

|                |     |                                                                    |  |  |

| 4              | App | olicative Languages in the Performance Evaluation of Algorithms 38 |  |  |

|                | 4.1 | The Evaluation of $\nu \mathcal{FP}$ Algorithms                    |  |  |

|                | 4.2 | Time-Space Tradeoffs                                               |  |  |

|                | 4.3 | Summary                                                            |  |  |

| 5 | $\mathbf{A}\mathbf{p}\mathbf{p}$ | plicative Languages in the Design of Algorithms                                        | 47  |  |  |  |  |  |

|---|----------------------------------|----------------------------------------------------------------------------------------|-----|--|--|--|--|--|

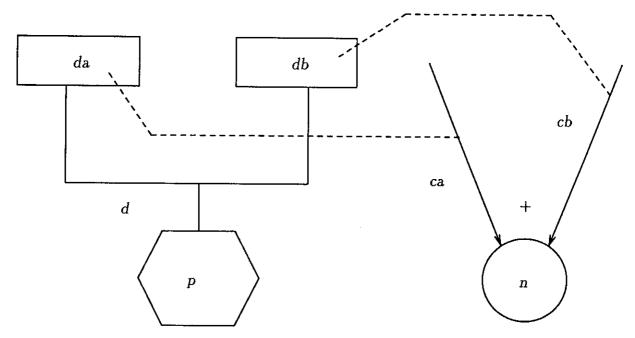

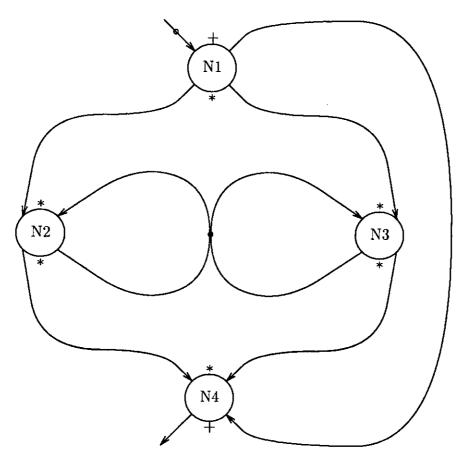

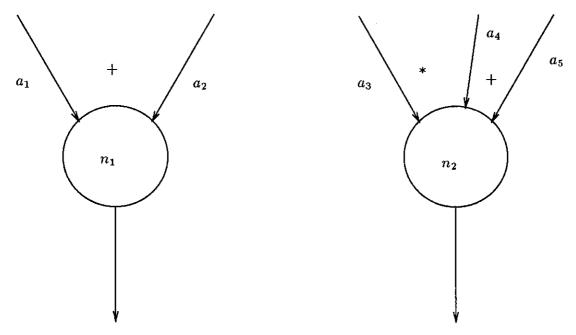

|   | 5.1                              | The Graph Model of Behavior                                                            | 48  |  |  |  |  |  |

|   |                                  | 5.1.1 The Control Domain                                                               | 48  |  |  |  |  |  |

|   |                                  | 5.1.2 The Data Domain                                                                  | 50  |  |  |  |  |  |

|   |                                  | 5.1.3 The Interpretation Domain                                                        | 51  |  |  |  |  |  |

|   |                                  | 5.1.4 The Token Machine                                                                | 52  |  |  |  |  |  |

|   |                                  | 5.1.5 Control Flow Analysis                                                            | 52  |  |  |  |  |  |

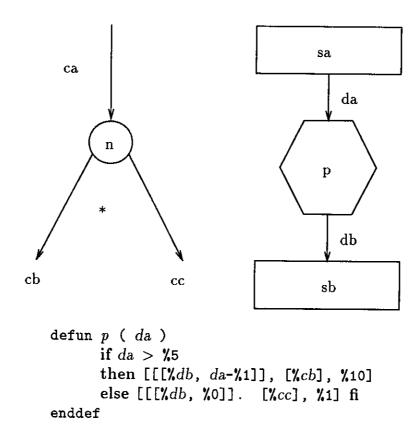

|   | 5.2                              | $ u\mathcal{FP} $ as an Interpretation Domain Language for the GMB $\dots \dots \dots$ | 53  |  |  |  |  |  |

|   | 5.3                              |                                                                                        |     |  |  |  |  |  |

|   | 5.4                              | Refinement via Transformations                                                         |     |  |  |  |  |  |

|   | 5.5                              | Equivalences between $\nu \mathcal{FP}$ Constructs and GMBs 60                         |     |  |  |  |  |  |

|   | 5.6                              | The GMB Refinement Procedure                                                           | 65  |  |  |  |  |  |

|   | 5.7                              | The GMB Abstraction Procedure                                                          | 68  |  |  |  |  |  |

|   | 5.8                              | Optimizations                                                                          | 68  |  |  |  |  |  |

|   | 5.9                              | Summary                                                                                | 73  |  |  |  |  |  |

|   |                                  |                                                                                        |     |  |  |  |  |  |

| 6 |                                  | olicative Languages in the Synthesis of Algorithms                                     | 75  |  |  |  |  |  |

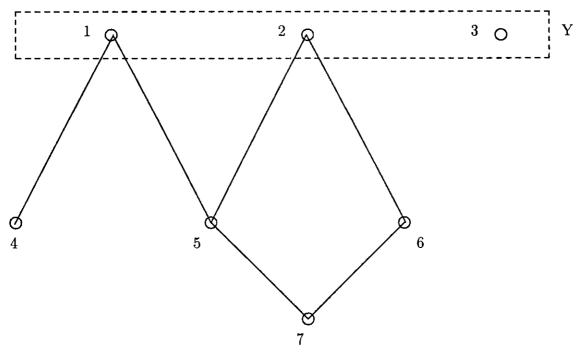

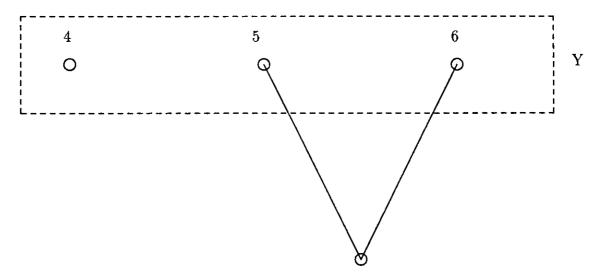

|   | 6.1                              | Overview of the Synthesis Process                                                      | 76  |  |  |  |  |  |

|   |                                  | 6.1.1 Classification of $\nu \mathcal{FP}$ Constructs                                  | 76  |  |  |  |  |  |

|   |                                  | 6.1.2 The Steps in Synthesis                                                           | 76  |  |  |  |  |  |

|   | 6.2                              | Specification and Design of Algorithms                                                 | 77  |  |  |  |  |  |

|   | 6.3                              | Space Domain Implementations of $\nu \mathcal{FP}$ Algorithms                          | 78  |  |  |  |  |  |

|   |                                  | 6.3.1 Restrictions                                                                     | 81  |  |  |  |  |  |

|   | 6.4                              | Time Domain Implementations of $\nu \mathcal{FP}$ Algorithms                           | 85  |  |  |  |  |  |

|   |                                  | 6.4.1 Restrictions and Extensions                                                      | 90  |  |  |  |  |  |

|   | 6.5                              | Formalizing Sequential Systems in $\nu \mathcal{FP}$                                   | 90  |  |  |  |  |  |

|   |                                  | 6.5.1 Formal Domains                                                                   | 91  |  |  |  |  |  |

|   |                                  | 6.5.2 Time Primitives and Axioms                                                       | 92  |  |  |  |  |  |

|   |                                  | 6.5.3 Example Proof                                                                    | 92  |  |  |  |  |  |

|   |                                  | 6.5.4 Identities                                                                       | 95  |  |  |  |  |  |

|   | 6.6                              | Interface to Layout Tools                                                              | 96  |  |  |  |  |  |

|   |                                  | 6.6.1 Cross-sections                                                                   | 96  |  |  |  |  |  |

|   |                                  | 6.6.2 Generating the Connectivity Information                                          | 100 |  |  |  |  |  |

|   |                                  | 6.6.3 Generating the Placement Information                                             | 100 |  |  |  |  |  |

|   | 6.7                              | Generating a Layout                                                                    | 103 |  |  |  |  |  |

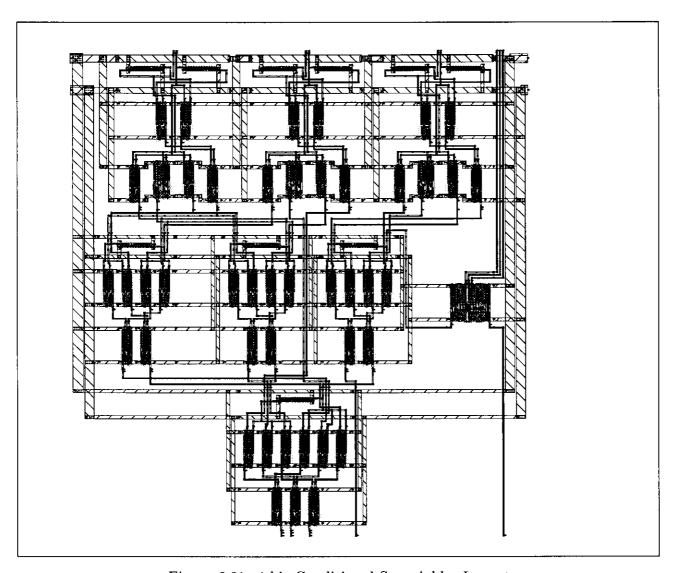

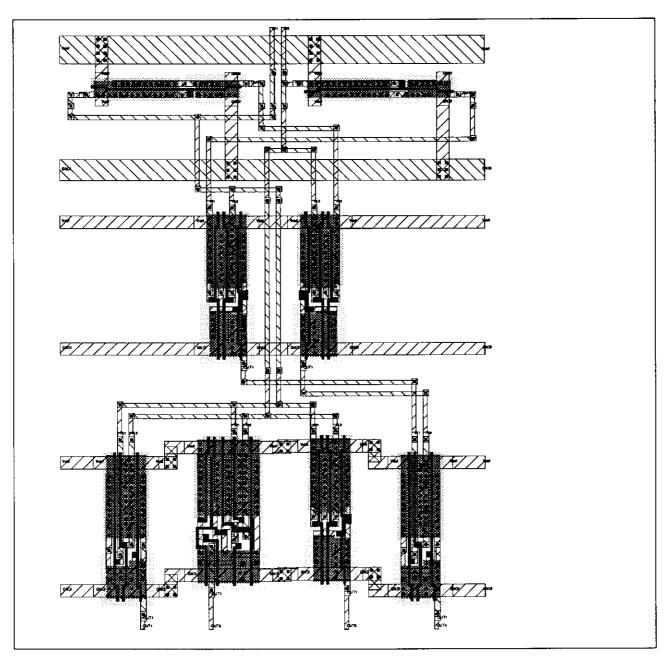

|   | 6.8                              | An Example: A Conditional-Sum Adder                                                    | 103 |  |  |  |  |  |

|   | 6.9                              | Summary                                                                                | 111 |  |  |  |  |  |

| 7 | Cor | nparison with $\mu$ FP                          | 112         |  |  |  |  |

|---|-----|-------------------------------------------------|-------------|--|--|--|--|

|   | 7.1 | Handling Sequential Circuits                    | 112         |  |  |  |  |

|   | 7.2 | Handling Initial State                          | 113         |  |  |  |  |

|   | 7.3 | Extracting Layout                               | 113         |  |  |  |  |

|   | 7.4 | Conditionals                                    | 114         |  |  |  |  |

|   | 7.5 | Bidirectional Flow                              | 114         |  |  |  |  |

|   | 7.6 | Combining Sequential Machines                   | 115         |  |  |  |  |

|   |     | 7.6.1 The Combinational Theorem                 | 115         |  |  |  |  |

|   |     | 7.6.2 Informal Proof                            | 116         |  |  |  |  |

|   |     | 7.6.3 Formal Proof                              | 117         |  |  |  |  |

|   | 7.7 | Summary                                         | 121         |  |  |  |  |

| 8 | Cor | nclusions                                       | 123         |  |  |  |  |

|   | 8.1 | Design Framework                                | 123         |  |  |  |  |

|   | 8.2 | The $\nu \mathcal{FP}$ Tools                    | 124         |  |  |  |  |

|   | 8.3 | Sequential Behavior via Space/Time Duality      | 124         |  |  |  |  |

|   | 8.4 | Synthesis via Transformations                   | 126         |  |  |  |  |

|   |     | 8.4.1 Space Synthesis                           | 126         |  |  |  |  |

|   |     | 8.4.2 Time Synthesis                            | 127         |  |  |  |  |

|   |     | 8.4.3 Generating Layouts                        | 127         |  |  |  |  |

|   | 8.5 | Transformations for Proving Equivalence         | 127         |  |  |  |  |

|   | 8.6 | Formalizing Aspects of GMB Semantics            | 128         |  |  |  |  |

|   | 8.7 | Applicative Specification Languages             |             |  |  |  |  |

| 9 | Fut | ure Work                                        | <b>12</b> 9 |  |  |  |  |

|   | 9.1 | Issues in Synthesis                             | 129         |  |  |  |  |

|   |     | 9.1.1 Transformations                           | 129         |  |  |  |  |

|   |     | 9.1.2 Expert System for Synthesis               | 130         |  |  |  |  |

|   |     | 9.1.3 Automated High-Level Test-Case Generation | 131         |  |  |  |  |

|   |     | 9.1.4 Extensions                                | 131         |  |  |  |  |

|   |     | 9.1.5 Typing, Scoping, and Extended Definitions | 132         |  |  |  |  |

|   |     | 9.1.6 User-specified Attributes                 | 132         |  |  |  |  |

|   |     | 9.1.7 General Placement of Inputs/Outputs       | 132         |  |  |  |  |

|   |     | 9.1.8 Different Sequential Structures           | 133         |  |  |  |  |

|   |     | 9.1.9 Different Timing Regimes                  | 133         |  |  |  |  |

|   | 9.2 | Issues in the GMB                               | 133         |  |  |  |  |

|   |     | 9.2.1 Improving Control Flow Analysis           | 133         |  |  |  |  |

|   |                               | 9.2.2 An Algebra for Logic Expressions                   | 3   |

|---|-------------------------------|----------------------------------------------------------|-----|

|   |                               | 9.2.3 Impact on Reduction                                | }4  |

| Δ | $\nu \mathcal{F} \mathcal{T}$ | Semantics 14                                             | ל'! |

|   | A.1                           | Objects                                                  |     |

|   | A.2                           | Application                                              |     |

|   |                               | Functions                                                | _   |

|   | 11.0                          | A.3.1 Selector Functions                                 |     |

|   |                               | A.3.2 Structure Modifying Functions                      | _   |

|   |                               | A.3.3 Predicate (Test) Functions                         |     |

|   |                               | A.3.4 Logical Conjunctions                               |     |

|   |                               | A.3.5 Arithmetic Functions                               |     |

|   |                               | A.3.6 Circuit (Gate-Level) Primitives                    |     |

|   |                               | A.3.7 Mathematical Library Routines                      |     |

|   |                               | A.3.8 Miscellaneous Functions                            |     |

|   | A.4                           | Combining Forms                                          |     |

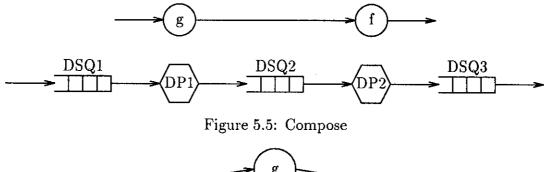

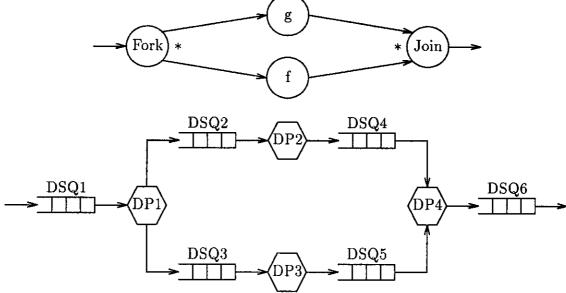

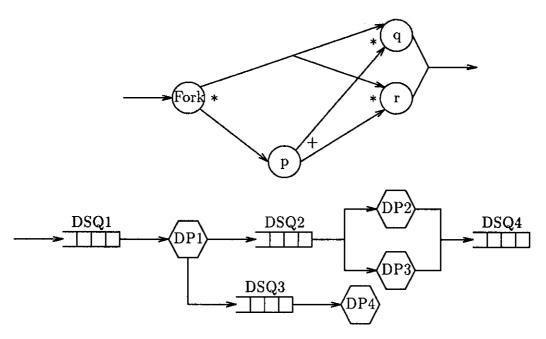

|   |                               | A.4.1 Compose                                            | 66  |

|   |                               | A.4.2 Construct                                          | 56  |

|   |                               | A.4.3 Apply-to-All                                       | 56  |

|   |                               | A.4.4 Conditional                                        | 57  |

|   |                               | A.4.5 Constant                                           | 57  |

|   |                               | A.4.6 Right Insert                                       | 57  |

|   |                               | A.4.7 Left Insert                                        | 58  |

|   |                               | A.4.8 Associative Insert                                 | 58  |

|   |                               | A.4.9 Tree Insert                                        | 58  |

|   |                               | A.4.10 Right Seq                                         | 59  |

|   |                               | A.4.11 Left Seq                                          | 59  |

|   |                               | A.4.12 Map                                               | 59  |

|   | A.5                           | Time Domain Primitives                                   | 60  |

|   | A.6                           | User Defined Functions                                   | 60  |

| R | Clar                          | ifications on Some Aspects of GMB Semantics              | 1   |

| _ | B.1                           | Introduction                                             |     |

|   | B.2                           | Semantics of Control Node Enabling                       |     |

|   | B.3                           | Semantics of Control Token Removal                       |     |

|   | B.4                           | Translation of Input Logic Expressions to Markings       |     |

|   | B.5                           | Semantics of Controlled-Read and Priority-Read Data Arcs |     |

|   | -                             | - · · · · · · · · · · · · · · · · · · ·                  | _   |

| B.6 | Incorporating Multiple Token Removal | 173 |

|-----|--------------------------------------|-----|

|     | Punion Theorem                       |     |

# Chapter 1

# Introduction

A discipline for complexity management is the key to the effective design of any large scale computer system, be it hardware or software [1, 2]. The design complexity in a large scale computer system comes from two major sources. The first is the large number of primitives involved. In the case of hardware, they could be transistors or chips. In the case of software, they could be lines of source code. However, a large number of primitives does not necessarily make for complexity. For example, a memory chip has a large number of transistors but is not necessarily complex.

A second source of complexity is the irregularity of connections or couplings between primitives. Traditional software design has been made simpler because the underlying model of computation has been a single sequential machine. In addition to handling concurrency, hardware design deals with the mapping of a design into a physical medium. This mapping has to be performed in the presence of constraints on power, space and time. The primarily two-dimensional nature of integrated circuits and the need to have direct physical connections between interacting modules makes the synthesis process even harder. These issues make the process of designing large scale hardware more difficult than that of software. However, lessons learned in software engineering can be applied to the hardware design process to address some of these problems.

This research concentrates on problems arising out of the process of designing hardware. A method, based on applicative languages, is proposed for the specification, evaluation and synthesis of hardware algorithms. Using the same language throughout the synthesis process leads to a coherent framework for design. Properties of applicative languages make them attractive for handling the complexity of large-scale design. The mathematical foundations of these languages enable the development of an algebra of programs that can be utilized both in the synthesis process and in proving properties about the designs.

The complexity of designing Very Large Scale Integration (VLSI) circuits can only be managed by the application of Computer-Aided Design (CAD) tools at all levels of the design process. In order to be effective, these tools must be flexible enough to be tailored to any specific design. Generally, VLSI CAD tools may be distinguished as being of either or both of two types: bottom-up composition tools or top-down synthesis tools. For bottom-up composition tools, the user either exactly specifies the placement of modules and the interconnections between them, or relinquishes control over the layout to the tool's algorithm. Examples of composition tools are graphic layout editors (e.g., Magic [3]) and placement and routing tools (e.g., PI [4, 5]). Top-down synthesis tools are capable of generating layouts from high-level specifications. Examples include various register-transfer silicon compilers that have been proposed and built [6, 7, 8].

Generally, these tools only provide an estimate of the area or delays of the circuit at the end of the synthesis process. That is, designers do not know the effects of their decisions on the performance until the design is complete. This makes the design process more batch-oriented rather than interactive. It also makes it difficult to explore alternative implementations and to evaluate objectively the alternatives with respect to user-specified criteria.

Small designs can be comprehended easily by a designer. As the size of designs grows larger it becomes more important to be able to formally prove properties about the design. Ideally, it should be possible to prove that the implementation meets the specification, but this is not always feasible. A formal basis for the representation of the design provides a means to reason about the representation.

In order to prove that the implementations match the specifications, the specifications themselves have to be generated in a suitable specification language. There are many kinds of specifications required in VLSI design. At highest level, the functional behavior of the algorithm is of interest. At lower levels it is the interfaces between modules and the interconnections between modules that are important. At the lowest level, it is the spatial positioning of modules and the geometry of their layout and interconnections that are important. At all these levels the timing of the design has also to be specified. At the higher levels the timing is abstract (e.g., sequencing), but at lower levels the specification of timing is more concrete (e.g., propagation and inertial delay).

Though most specifications tend to be described in textual languages, VLSI design, especially at the lower levels, is oriented towards layout on silicon and hence spatial in nature. The design process would be aided if a visual representation of the specifications and the implementations were provided at all levels of abstraction.

In the following sections, each of these issues is taken up in turn. Various problems are exposed and their solutions discussed.

# 1.1 Complexity Management

This section explores some methods that are useful in managing complexity in VLSI design.

#### 1.1.1 Abstraction

Using a computer language for description makes any description more precise since these languages have specific semantics. In addition, using a language description for an intuitive process aids in the documentation of that process by providing a written description of what the designer envisions. Some languages (e.g., Ada¹) also provide the ability to separate the interface of a function from the body of the function. This capability allows the concerns of describing the interface to be treated separately from the concerns of designing the body. All languages provide some form of abstraction. An abstraction is a simplified description, of a system that emphasizes some of the system's details or properties while suppressing others. A good abstraction is one that emphasizes details that are significant to the reader or user and suppresses details that are, at least for the moment, immaterial or diversionary [9]. One useful example of abstraction that is commonly found in computer languages is functional abstraction where a particular process, used with different parameters, is abstracted with respect to those parameters, to form a function. Timing or type abstraction are examples of other kinds of useful abstractions.

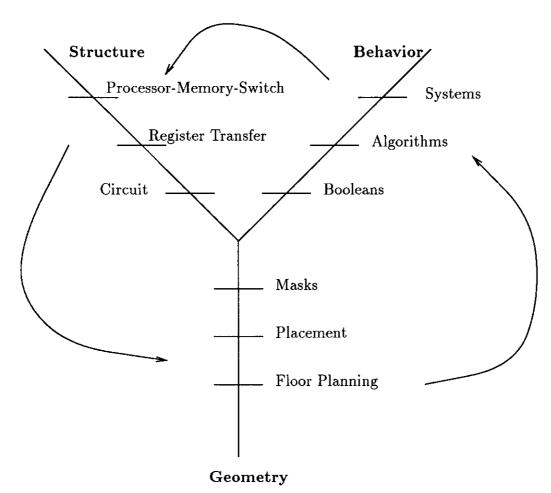

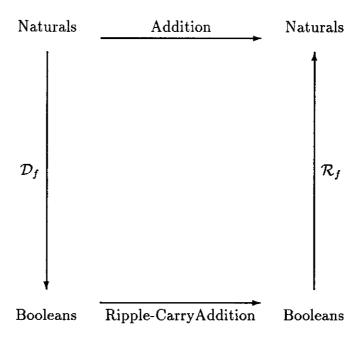

The process of designing Integrated Circuits (ICs) can be described by the Gajski-Kuhn Y-chart [10] (figure 1.1) where each axis signifies one representation of the circuit. The representations towards the center of the chart are less abstract than the ones towards the outer edges. The synthesis process starts at the most abstract behavioral representation and ends at the most concrete geometric representation. The actual path followed is dependent on the particular synthesis method employed. Thus we see that in the VLSI domain there are three main classes of abstractions—structural, behavioral and geometric.

#### Structural Abstraction

Structural abstractions deal with the composition and interconnection of modules at one level of abstraction to construct a module at a presumably higher level of abstraction. Language designers have taken different approaches to the problem of describing such relationships.

One approach is "connection-oriented" in the sense that it explicitly specifies which terminal is to be connected to which other terminal. This is equivalent to using a net-list to describe

<sup>&</sup>lt;sup>1</sup>Ada is a trademark of the US Department of Defense (Ada Joint Program Office).

Figure 1.1: Gajski-Kuhn Y-chart

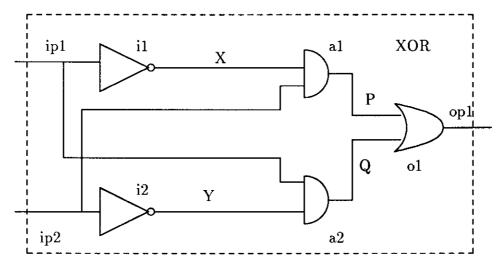

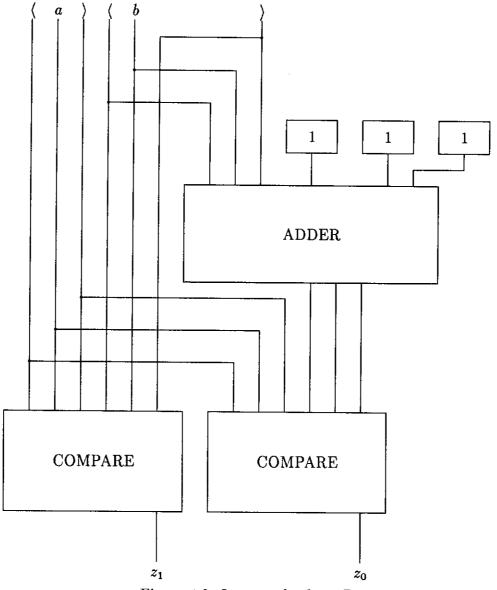

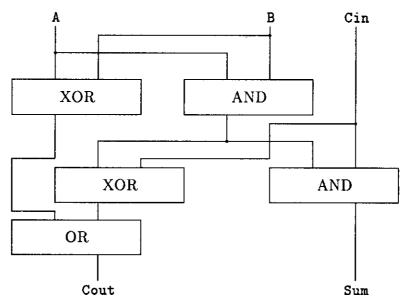

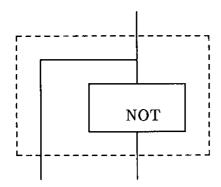

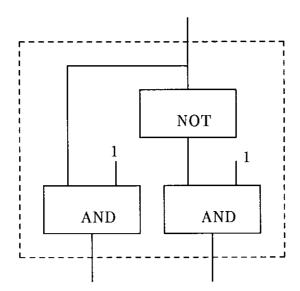

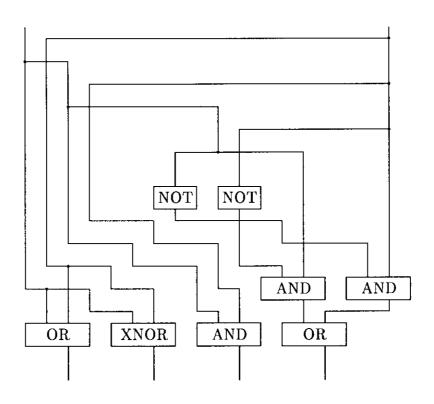

Figure 1.2: XOR gate implementation

the connections. Hardware design and description languages like SILAGE [11] and ELLA<sup>2</sup> [12] use such an approach. For example, an exclusive OR gate implementation shown in figure 1.2 could be described by the ELLA program in figure 1.3 (taken from [13]). The MAKE statement specifies the component modules of the current module and the JOIN statement specifies which connections are made. For example,

$$(i1, ip2) \rightarrow a1$$

means that the output of i1 and the input terminal ip2 are to be connected to the two inputs respectively of the module a1.

Concurrent Prolog [14, 15] uses a similar approach but it names each connection and thus does not explicitly specify the endpoints of each connection. For example, the ELLA example in figure 1.3 could be written in Concurrent Prolog as shown in figure 1.4. The basic model of Concurrent Prolog is that of processes communicating through ports and thus this is a good match to the requirement of describing interconnected modules. This approach allows arbitrary connections to be specified between terminals. Though this makes the approach very powerful, it is not structured and can lead to situations that are difficult to analyze. However, CIRCAL [16, 17] provides a formal basis for describing interconnections between modules and a mechanism for structural abstraction by abstracting away internal ports and connections.

Another approach specifies connectivity implicitly. Functions correspond to modules. Parameters correspond to input ports and result values to output ports. The call graph of the

<sup>&</sup>lt;sup>2</sup>ELLA is a trademark of the UK Secretary of State for Defense.

Figure 1.3: Explicit ELLA description of XOR

```

XOR(ip1, ip2, o1) :-

INV(ip1, X),

INV(ip2, Y),

AND(X, ip2, P),

AND(ip1, Y, Q),

OR(P, Q, op1).

```

Figure 1.4: Concurrent Prolog description of XOR

```

FN XOR = (bool: ip1 ip2) -> bool:

OR( AND(INV(ip1), ip2),

AND(ip1, INV(ip2)) ).

```

Figure 1.5: Implicit ELLA description of XOR

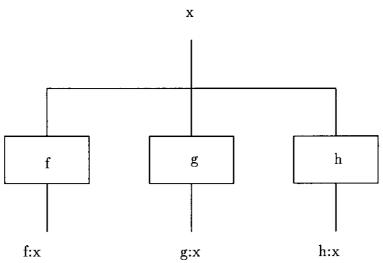

functions corresponds to the structural hierarchy of the modules. The naming of parameters corresponds to the interconnections between the modules. Languages like  $\mu$ FP [18] and  $\nu$ FP (described in [19] and this dissertation) follow this approach. SILAGE and ELLA support both approaches. For example, an implicit version of the ELLA description of the XOR gate in figure 1.2 is shown in figure 1.5. Though this approach makes it easy to analyze the behavior of the resulting connections, it is less powerful than the connection-oriented method. For example, it is not possible to describe cross-coupled NAND gates in this manner.

Languages like VHDL<sup>3</sup> [20] and Standard ML (SML) [21, 22] allow the designer to separate the concerns regarding the specification and checking of interface descriptions and the design of the body of the functions. In such languages the module hierarchy can perform the role of the structural hierarchy. For example, in VHDL, the interface description of the XOR gate could be described as shown in figure 1.6 and the body of an implementation corresponding to figure 1.2 is shown in figure 1.7.

Replication of cells to form regular structures is provided for in all the languages mentioned above. VHDL provides the *generate* statement, ELLA provides the *replicator* construct and  $\mu$ FP and  $\nu \mathcal{FP}$  use the *insert* form.

The constructs provided by  $\nu \mathcal{FP}$  for structural abstraction are mentioned in chapter 2 which also gives an overview of the  $\nu \mathcal{FP}$  system. The use of these constructs is shown in chapter 6 and a comparison with  $\mu FP$ 's structural constructs is taken up in chapter 7.

#### Behavioral Abstraction

Behavioral abstraction groups behaviors together to form other behaviors at a higher level of abstraction. Behavior can be separated into the functional aspects (i.e., what function is performed by this module) and the timing aspects. In some cases, this separation can not be made cleanly since the function performed by the module might well depend on the timing of submodules.

<sup>&</sup>lt;sup>3</sup>VHDL is a trademark of the US Department of Defense.

Figure 1.6: VHDL interface description of XOR gate

Functional abstraction is provided by all programming languages. However, only some of them allow easy composition of behaviors in a way that is guaranteed not to introduce unwanted interactions. This issue is taken up in more detail in section 1.1.2. FP is one language that provides for easy composition and the XOR gate example of figure 1.2 can be described as shown in figure 1.8. It shows how to combine the behaviors of AND gates, OR gates and inverters to result in the behavior of an XOR gate. Though pure CIRCAL only provides a mechanism for structural abstraction, an extension called TYPED CIRCAL [23] also allows data abstraction to be treated in a formal framework.

Another important benefit of behavioral abstraction is the ability to evaluate, simulate, verify or manipulate a cell at different levels of abstraction. For example, a transistor could be described as a rather detailed SPICE [24] model to evaluate its low level timing behavior. Then, transistors could be grouped together to construct a NAND gate. Once the characteristics of the NAND gate have been determined using the characteristics of its component transistors, it is no longer necessary to retain all the lower-level information about the transistors. It is possible to now use the NAND gate as a higher-level logical entity with a functional behavior in terms of boolean algebra (or, at least, discrete logic levels corresponding to booleans) and with a timing behavior in terms of a propagation delay. A simulator capable of using descriptions at various levels of abstraction simultaneously is described in [25].

```

architectural body GATE_DESC_OF_XOR of XOR_GATE is

component AND_GATE (A,B: in BIT; OUT: out BIT);

component INV_GATE (A: in BIT; OUT: out BIT);

component OR_GATE (A,B: in BIT; OUT: out BIT);

signal X,Y,P,Q: BIT; -- internal signals

begin

i1: INV_GATE (ip1, X);

i2: INV_GATE (ip2, Y);

a1: AND_GATE (X, ip2, P);

a2: AND_GATE (ip1, Y, Q);

o1: OR_GATE (P, Q, op1);

end GATE_DESC_OF_XOR;

```

Figure 1.7: VHDL body for XOR gate

```

or °[ and °[ inv °1, 2],

and °[ 1, inv © 2]]

```

Figure 1.8: FP description of an XOR gate

Timing in VLSI design needs to be specified in many ways. At the highest levels of abstraction, all that is required is the specification of sequencing information. That is, only the dependencies between computations need to be specified. As the algorithm is mapped to specific hardware, more concrete timing is specified, especially in a synchronous system. In particular, each computation will typically be mapped to a specific element of a time sequence in such a way that the original precedence constraints are satisfied. At still lower levels, each element of the time sequence is mapped to a particular point on a concrete time scale. This implies that the absolute delays associated with each computation have to be specified. These can be specified as inertial, transport or propagation delays.

There are many different models of time that are used by various languages. These models can either be asynchronous or synchronous. VHDL, for instance, uses a synchronous model of time that is similar to that used in CONLAN [26], with a macro and micro time scale. The micro time scale is measured in discrete units and is used to represent real time. The macro time scale denotes the unit delay of the cell and is not measurable. A macro time step can contain any number of micro time steps, and the number of micro time steps contained in each macro time step need not be the same. This allows the designer to simultaneously model the timing behavior at two levels of abstraction.

Interval Temporal Logic (ITL) [27, 28] allows the specification of digital circuits with a discrete sequential model of time. ITL is an extension of temporal logic, itself an extension of predicate logic, to handle dynamic behavior. Time is split up into discrete intervals and changes in values of signals are allowed only at interval boundaries. ITL makes no assumptions on the lengths of these intervals. In particular, they all do not need to be the same length. Thus, in addition to the normal process of data abstraction, it is also possible to specify timing at different levels of abstraction. ITL does not provide any way to specify time in actual units.

TYPED CIRCAL [23] introduces timing abstraction into pure CIRCAL. This allows the representation of a hierarchy of clocks where n clock ticks of a particular clock can be replaced by one clock tick of a less frequent and more abstract clock. Pezzé [23] shows how to use time conversion to convert a representation from one clock to another. In TYPED CIRCAL timing abstraction is dependent on data abstraction and both may need to be performed to verify that a particular implementation meets its specification. The time synthesis procedure described in section 6.4 follows a similar approach which results in hierarchically nested clocks.

Concurrent Prolog [15] describes processes communicating via streams connected to ports. At each level of abstraction, a circuit block is represented as a predicate and the wires connecting them are represented as the parameters of that predicate. Each parameter is treated as an infinite stream which represents the stream of values on that wire. Synchronization is performed by declaring some uses of a parameter as read-only. In this case, expressions using the read-only parameter will block until the value of the parameter has been instantiated. It is

not possible to directly specify timing in Concurrent Prolog. However, a clock can be modeled as an infinite sequence of ascending natural numbers. This stream has to be explicitly fed to every circuit that uses it. Each circuit can then synchronize itself with this stream by using it as a read-only parameter. In this sense, it can be said that Concurrent Prolog uses a sequential model of time. This is only true if such a "clock" stream is used. Otherwise, the language is relational and has no inherent notion of time.

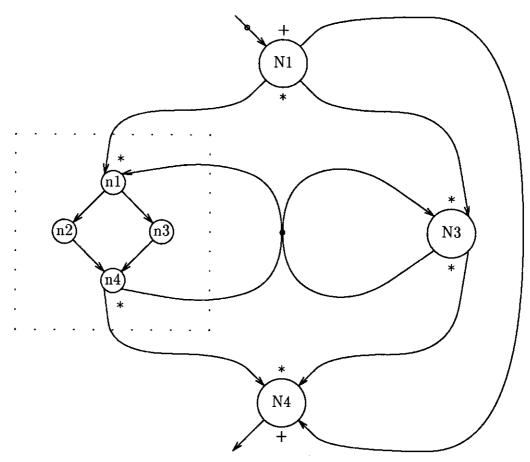

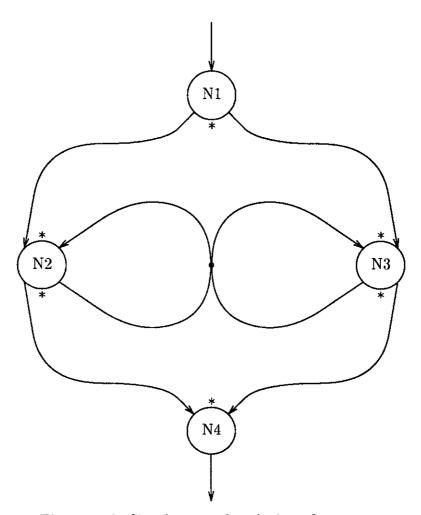

The Graph Model of Behavior (GMB) [29] is an extension of Petri Nets [30] and is particularly useful to model concurrent asynchronous events. This model is event driven and does not have any inherent notion of synchronous behavior. All that it can specify is the precedence between events. However, synchronous behavior can be modeled, just as in Concurrent Prolog, by making the clock explicit and feeding it to each circuit that requires it.

Chapter 2 describes  $\nu \mathcal{FP}$  constructs that can be used for behavioral abstraction. Examples of their use are provided in chapter 6 which also shows how to introduce sequential behavior into  $\nu \mathcal{FP}$ .

#### Interaction between Structure and Behavior

Each system has different ways of describing structure and behavior. Some systems such as VHDL use different constructs in the same language to describe the structure and behavior. For example, the architectural body construct is used to describe the structure, and the behavioral body construct is used to describe the behavior.

Design systems such as the Systems ARchitect's Apprentice (SARA) [29] provide a separate language to describe the structure of the design and a different language to describe the behavior. The SARA system also provides a mechanism to map the behavior to the structure. In fact, it is possible to map different behaviors to the same structure. This is similar to VHDL's mapping of different behavioral bodies to the entity interface description.

It has been suggested [2] that a structured design methodology for VLSI should have a one-to-one mapping between behavior and structure in order to manage the complexity.  $\nu \mathcal{FP}$  and  $\mu FP$  take this approach. The notions of structural and behavioral specification are tightly integrated in these systems. During the design process, a particular description can be treated either as behavioral or structural depending on what the designer wants to emphasize at that time. For example, the description in figure 1.8 can be taken to mean that the behavior of an XOR gate can be specified in terms of the behavior of AND gates, OR gates, and inverters as shown in the figure; or it can mean that an XOR gate can be constructed structurally out of AND gates, OR gates and inverters as shown in the figure. In  $\nu \mathcal{FP}$ , the interpretation chosen is dependent on whether the module is tagged as a primitive at this level of abstraction. If it is tagged as a primitive, then its internals are treated as strictly behavioral by the system. If not,

```

behavioral body XOR_BEHAVIOR of XOR_GATE is

begin

op1 <= ip1 xor ip2 after 35ns;

end XOR_BEHAVIOR;</pre>

```

Figure 1.9: Behavioral description of XOR gate in VHDL

```

architectural body XOR_STRUCTURE of XOR_GATE is

component NAND_GATE (A,B: in BIT; C: out BIT);

signal X,Y,Z: BIT; -- internal signals

begin

n1: NAND_GATE (ip1, ip2, X);

n2: NAND_GATE (ip1, X, Y);

n3: NAND_GATE (X, ip2, Z);

n4: NAND_GATE (Y, Z, op1);

end XOR_STRUCTURE;

```

Figure 1.10: Alternate structural implementation of XOR gate in VHDL

then the internals are treated as a structural combination of modules. Chapter 4 demonstrates this with an example.

However, structure and behavior are independent and conceptually orthogonal and it is possible to change the structural hierarchy without changing the behavioral hierarchy. For example, figure 1.7 and figure 1.10 show two different structural implementations of the XOR gate whose behavior is specified in figure 1.9 and which meet the interface specifications of figure 1.6. In the case that the structural and behavioral hierarchies are distinct a mapping between the two has to be provided [31, 32]. It is not clear which approach is better in all situations. When the design complexity is high, experience shows that the payoffs of using the former approach compensates for the attendant loss in flexibility.

#### Geometry Abstraction

The third domain of abstraction in VLSI is that of geometry. At the lowest levels geometry consists of overlapping rectangles of different colors representing the different layers on a silicon

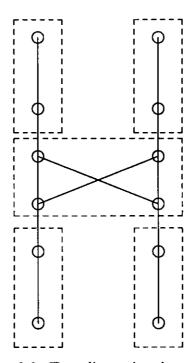

chip. At the next higher level, the rectangles can be combined in particular fashions to form transistors or other circuit elements. Circuit elements are combined together to form cells. Reusable cells (e.g., gates, adders, ALUs) can be placed in a library for use by designers. Such cells are treated as fixed size rectangles containing geometry with ports on the edges. These ports have a fixed location with respect to the cell and are in a particular silicon layer. In some systems, it is possible to stretch cells either in the vertical or horizontal direction along specific cross-sections. In those cases, the rectangles that are cut by the cross-sections are extended as necessary to effect the stretching of the cell. This is done in order to match the pitch of adjacent cells so that the interconnections between them can be achieved via abutment rather than routing. A designer can now use this as a piece of rectangular geometry without being concerned about the geometry contained inside. For example, there is no need to re-verify that design rules are satisfied inside the cell when the cell is used in conjunction with other cells in a design. Depending on the design, it may still be necessary to check for design rule violations at the edges and at the ports. A procedure for analyzing a hierarchical geometric description and filtering out only the parts that need to be checked is described by Whitney [33]. Cells may be combined with other cells and connecting rectangles to form other higher-level cells of geometry.

The consistency checking task is eased if a separated hierarchy [34] is used. A separated hierarchy is one in which the representation-dependent information is only present in leaf cells. All the other cells are composition cells. Composition rules must be established to determine how to implement a composition cell within the given representation. In such a system, only the leaf cells and the composition rules need be checked instead of all the geometry. Rowson, in [35], describes a rigorously defined and efficient composition rule.

An applicative framework can be used in different environments by just changing the set of primitives used and possibly the combining forms. Henderson [36] describes an applicative system for describing geometry and for combining pieces of geometry in different ways. The  $\mu$ FP system uses this system as a back-end for generating layouts suitable for VLSI implementation.

## 1.1.2 Composition

Another way to manage complexity is to provide a formal way of combining smaller pieces into larger ones. Most systems provide for ad hoc combining of modules. However, these methods do not guarantee any properties of the combination and hence it is difficult for the designer to treat the combination as a module without a thorough analysis of the components. For example, it is not possible to arbitrarily combine VHDL entities without analysis because they may refer to global constructs. If the global constructs used independently by the constituents conflict in some way, the designer will be faced with unwanted interactions between the constituents.

These interactions cannot be checked for by just examining the interfaces of the modules being combined, but the behavioral body of each will have to be analyzed completely before a claim of non-interference can be made. The use of packages alleviates but does not eliminate this problem.

In contrast, it is possible to combine a  $\nu \mathcal{FP}$  description of a module with any other  $\nu \mathcal{FP}$  description and to be guaranteed that they will not interfere with each other because systems like  $\nu \mathcal{FP}$  are free of side-effects. In addition, proven laws about  $\nu \mathcal{FP}$  combining forms may be used to reason about the behavior of the combined whole if the behavior of the constituent parts is known. Systems proposed by Cardelli [37] and Milne [38, 17] demonstrate mathematical formalisms for describing networks of interconnected modules. They also provide methods for formally reasoning about combinations of interconnected modules that form higher-level modules.

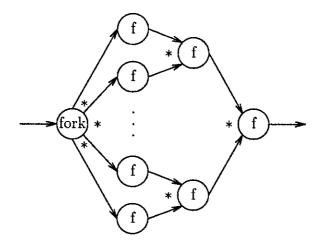

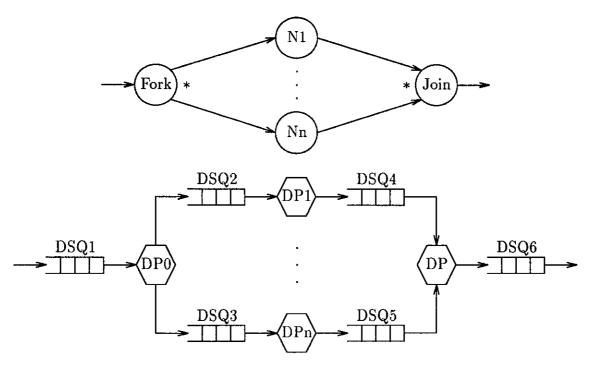

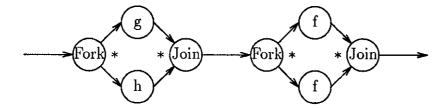

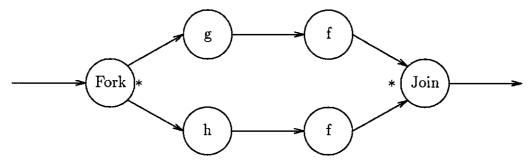

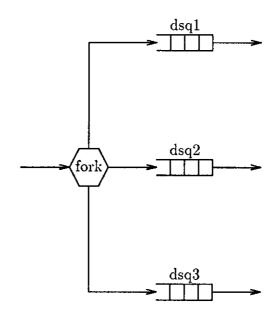

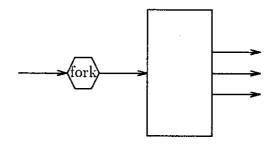

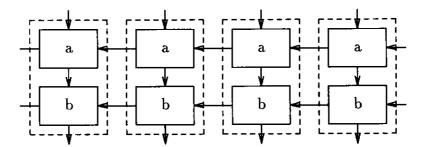

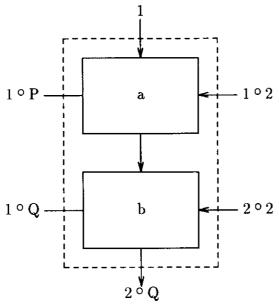

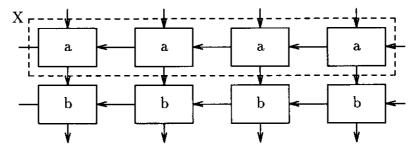

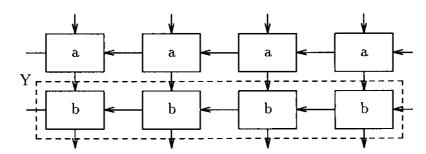

In general, modules can be connected in any ad hoc manner as long as the port constraints are satisfied. For example, it is syntactically valid to connect modules together as long as an input port on one module is connected to an output port of another. However, in many cases, designers use certain regular or structured combinations or idioms. For example, cell-iterative or parallel arrays are often used in regular design. Languages like  $\nu \mathcal{FP}$ ,  $\mu \text{FP}$  and AHPL [39] provide convenient combining forms to be used in such situations. More than providing convenience, the structured nature of these connections allows  $\nu \mathcal{FP}$  to prove theorems that can be used to deduce properties of the combination given the properties of the cell. Chapter 2 documents the combining forms available in  $\nu \mathcal{FP}$ . Some of the more useful forms are diagrammed in Chapter 6. Section 7.6 shows how the behavior of the composition of two sequential machines can be derived from the behavior of the individual machines.

### 1.1.3 Design Framework

Complexity can be managed effectively if all the various levels of the design process are carried out within a coherent design framework. A design framework can help in the integration of tools. There are two approaches to providing coherence. One way is to use the same language to describe the design at all levels of abstraction. This approach has the advantage that the designer has to learn only one language. Additionally, it provides coherence by using the same language throughout the design process.  $\nu \mathcal{FP}$  uses this paradigm. Chapter 8 describes the components of the  $\nu \mathcal{FP}$  system.

The other approach is to use different languages to represent the design at each level of abstraction. The advantage of this approach is that each language can be tailored for that level of abstraction. The semantic gap, between the concepts used by the designer at that level and the constructs supplied by the language, can be reduced by an appropriate choice of

constructs. In addition, the framework usually provides a common data representation that is used by each tool to communicate with other tools. The set of OCT tools [40] from the University of California at Berkeley is one example of such a framework.

#### 1.2 Tools

Design tools often are overly specific in their domain of applicability. Often they are constructed that way because they are application-specific. It is much better to make a general design tool that can be tailored to the application area. The basic framework can then be shared among various application-specific tools. Another way to increase the domain of applicability of a tool it to make it extensible. Most tools are not and this make them frustrating to the user. The problem is that the tools are fine as long as the problems being addressed are what had been envisioned by the designer. Often enough, however, users are faced with problems that are just slightly different than what had been envisioned by the tool designer. In this situation, most tools prove to be inflexible and unusable. The solution is to provide tools which exist in a framework that can be easily extended by the user to cover the cases the existing tools do not.

One approach to extensibility is to use an embedded language. One of the earliest VLSI tools was LAP [41] which embedded drawing commands in SIMULA [42]. Thus, with very little effort, it was possible to create a VLSI layout system with the full power of SIMULA. The DPL/Daedalus [43] system takes a similar, but more sophisticated approach by embedding a description and constraint system in LISP [44]. Macpitts [6] and its commercial descendent MetaSyn [45], are also embedded in LISP but have typed variables and allow user extensions. The  $\nu \mathcal{FP}$  system is user-extensible and tailorable. Users can extend the primitive function set to suit their requirements. In addition, the  $\nu \mathcal{FP}$  framework is applicable to different domains by just changing the primitive function set and combining forms as required. Chapter 2 describes the primitives and functional forms of the  $\nu \mathcal{FP}$  system.

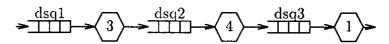

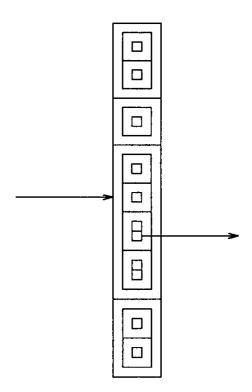

The most common instances of application-specific languages and systems are those developed for Digital Signal Processing (DSP). The FIRST silicon compiler [46] was a system that was developed to generate bit-serial implementations of DSP algorithms. The language SILAGE [11] used in the LagerIV [47] and CATHEDRAL [48] systems, and LUSTRE [49] have been developed to describe and synthesize regular DSP algorithms.

# 1.3 Exploring Alternative Designs

The systems mentioned above do not provide any estimate of the area occupied or the delays experienced by the circuits synthesized. It is only at the end of the synthesis process that these performance criteria are available. This means that designers have to wait until the end of the synthesis before recognizing the effect of their design decisions on the performance of the circuit being designed. Therefore, it becomes difficult for the designer to rapidly evaluate alternative design strategies for the particular application. It is possible to provide designers with estimates of various performance parameters at all stages of the design process and at all levels of abstraction. Obviously, at the higher levels of abstraction, these estimates will be less accurate because the exact details of the particular implementation strategy will not be known. However, these estimates are useful in order to provide the designer with enough information to make go/no-go decisions with the particular approach. For example, after describing the algorithm at a high level, the system may estimate that it will take two orders of magnitude more area than is available. Clearly, the designer can benefit from such information and can take early remedial action and try out other approaches.

This method of design allows the designer to perform rapid prototyping of alternative implementations at all levels of abstraction, leading to a design that is more suitable under the given design requirements.  $\nu \mathcal{FP}$  provides such a system and evaluation mechanisms. Not only must there be a way to evaluate performance criteria at all levels of abstraction, but this evaluation must be fast and must not involve prohibitive overheads. If the evaluation takes too much time, users will tend not to use the features.

During the formulation of design alternatives, the designer has to be sure that each of the alternatives actually implements the same specification. One way of guaranteeing this is to take a transformational approach as in [50]. In this system, transformations are applied to the original specification to generate the various alternatives. These transformations are guaranteed to maintain the semantics of the specification. Chapter 4 demonstrates how this is approach is used in  $\nu \mathcal{FP}$  to evaluate alternate designs.

## 1.4 Reasoning about Designs

Most of the design systems available today have representations of the design that are not amenable to easy verification. The problem consists of proving that two descriptions are equivalent in some sense. Usually the two descriptions are at different levels of abstraction. One is a description of a specification and one is the description of a particular implementation of that specification. Often the criterion for equivalence is that the input-output behavior

of the two descriptions is the same. That is, for the same inputs, both the descriptions will produce the same outputs. Sometimes the descriptions may be at the same level of abstraction but may represent different views of the same design. In this case, the equivalence criterion is usually to show that one aspect of the descriptions (say, the control flow) is the same in both descriptions. Chapter 5 shows how  $\nu \mathcal{FP}$  transformations can be used to prove equivalences between different views during the design process.

In order to be able to prove such equivalences, the semantics of the descriptions must be provided. These semantics can then be reasoned about. There are two ways of conducting this reasoning. One way is to use the semantics of the descriptions to obtain the denotation of each. Formal methods can then be used to show that the two denotations are equivalent. This is the approach taken in [37, 17, 23]. The other approach is to use transformations to transform one description to another. If these transformations have previously been shown to maintain the equivalence property, whatever it may be, then the two descriptions can be shown to be equivalent. ITL,  $\mu FP$ , and  $\nu FP$  use this approach. The Yorktown Silicon Compiler [51] also makes use of transformations at specific stages in the silicon compilation process. The advantage of using this method is that the proof is carried out in the same domain as the descriptions and there is no need to involve another domain (that of denotations) in order to prove properties about the descriptions. The disadvantage is that the kind of properties that can be proved are restricted to the set of transformations provided. This can be alleviated by admitting new transformations into the system, but if these new transformations cannot be deduced from already existing ones, then it will usually be necessary to prove the new transformations by appealing to another domain. Chapter 6 gives various examples of transformations used for synthesis in  $\nu \mathcal{FP}$ . As an extended example of the use of such transformations, section 7.6 demonstrates the use of transformations to derive the proof of a theorem about combinations of sequential machines.

## 1.5 Specifications

In order to prove equivalence between a specification and implementation, it is necessary to construct a specification first. This specification is written in a specification language. An implementation at one level can be thought of as a specification for the next lower level. It is therefore necessary to have specifications at all levels of abstraction. Any specification should be minimal. That is, it should specify only those properties that are relevant at that level and no more. At the highest (algorithmic) level of specification, it is particularly important that the minimum amount of sequencing be specified. This implies that there are no extra sequencing constraints in the specification other than those necessary for the proper operation of the

system. An applicative language like  $\nu \mathcal{FP}$  or  $\mu FP$  fits these constraints well because the only sequencing that is specified is that the input data must be available before the computation can start. The Church-Rosser property of applicative languages [52, 53] allows even more flexibility in sequencing. The Church-Rosser property states that the order of evaluation of its sub-expressions does not change the meaning of the whole expression. Therefore, the order of evaluation of sub-expressions is not constrained.

Structural specifications consist of specifying modules that encapsulate behavior. Behavior is only visible to the outside world via ports. Modules may be combined by connecting their ports together. In order to facilitate this composition, it would be useful if the ports could be typed or otherwise possess attributes. With that information, it is possible for a composition system to check that the ports being connected are compatible. The simplest example of such checking is the type-checking performed between a called function and the arguments passed to it. In order to be flexible, typing and checking should be polymorphic. Languages like SML [54] provide such static type-checking.  $\nu \mathcal{FP}$  currently uses run-time type-checking and so type errors are only detected at run-time. However, this is not inherent in the language and the addition of a type system is suggested as future work.

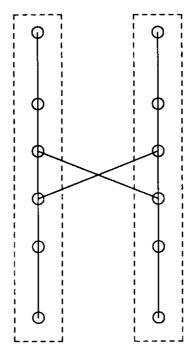

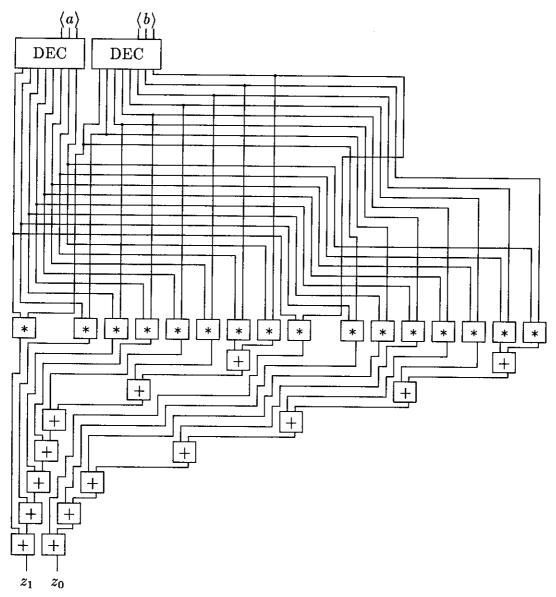

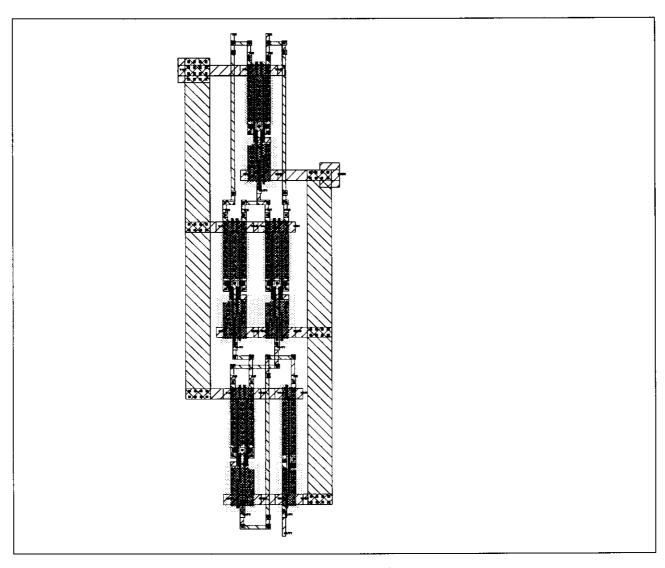

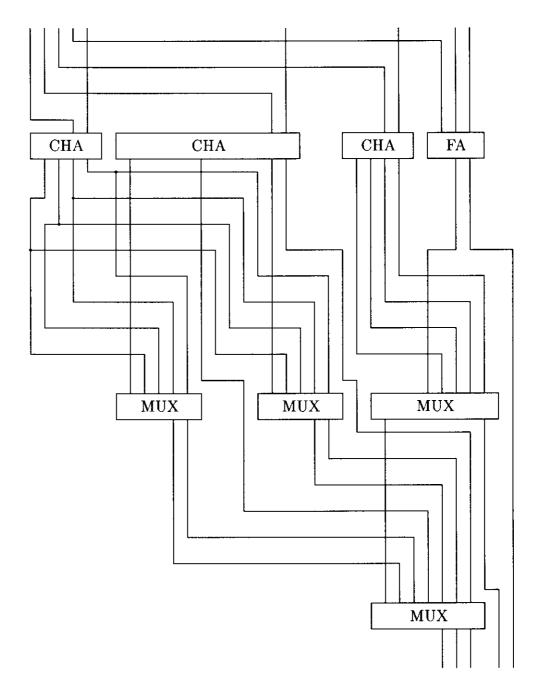

At lower levels of abstraction the spatial positioning between components is important. It can be specified in different ways. One is by just specifying topology. That is, which ports on certain modules are connected to which ports on other modules. In addition to this connectivity information, some relative placement information can also be specified. This consists of specifying which modules are on which side of a certain module. Further positioning information can be specified by specifying geometry. That is, actual locations, either absolute or relative to some other point, are specified. The  $\nu \mathcal{FP}$  system is capable of specifying and displaying relative placement information. Schlag, in [55], shows how this information is extracted from the specification. Chapter 6 shows the specification of structure and behavior in  $\nu \mathcal{FP}$ . Chapter 3 explores the use of applicative languages, and  $\nu \mathcal{FP}$  in particular, in the specification of algorithms at the highest levels.

#### 1.6 Visual Feedback

VLSI design is a graphical process—especially at the lower levels which deal with the geometry of the layers in silicon. Most of the lower level layout tools are visual, but higher level tools like silicon compilers are often textual. Intermediate tools like floor planners tend to be graphical or both graphical and textual. What is needed is to have visual feedback at all levels of abstraction, for the same reasons as it is good to have performance feedback at all levels of abstraction. For instance, suppose there is a description of the algorithm at a high level that

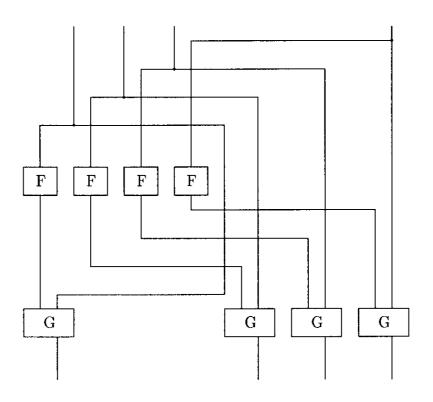

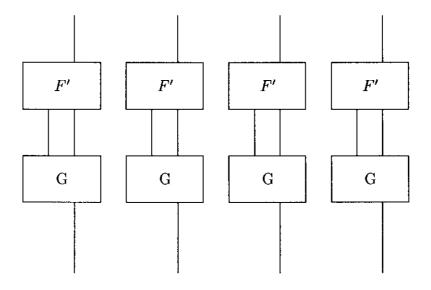

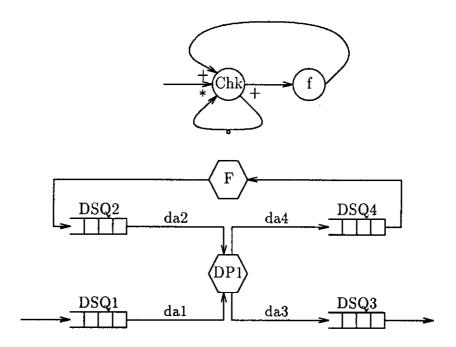

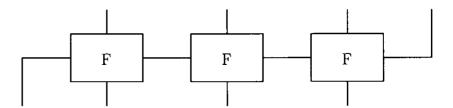

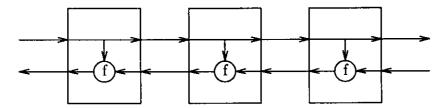

Figure 1.11: Blocks with routing outside

Figure 1.12: Blocks with route-throughs

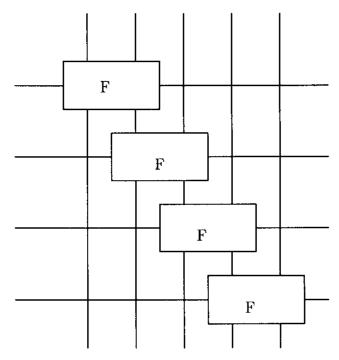

implied a lot of routing around a block to get to another block. If designers could see the layout or routing implications of their high level decisions, they would be able to modify their approach to take this into consideration. For example, in the previous case, the designer could consider using cells that routed the extra wires through the cells of the first block rather than around it. Figure 1.11 shows how the layout would look like with the routing around the cell. Figure 1.12 shows that the routing area has been saved by having the wires pass through the cell F'. F' is a cell that is the same as F except that it additionally routes its input to another output. A simple transformation is used to prove the equivalence of the two representations.

A graphical language is very useful at the geometry and layout planning levels of the design since most of the information at those levels is pictorial in nature. Hence there is a better match between the objects used for description and the objects being designed—the semantic gap is small. These languages also provide a better human-machine interface at these levels. Textual languages are better at specifying algorithmic behavior and therefore more useful at higher abstraction levels. They also provide an easier interface between different tools since the interface can be plain text.

Both kinds of languages also have their deficiencies. Visual languages are limited in what they can easily specify and are often forced to revert to a textual mode to specify complex functions. Since visual systems are required to show the current picture, structuring or abstraction information is either not allowed to be specified or it is hidden from the user. Often different

parts of a picture are supposed to bear a spatial relationship to each other. However, unless this relationship is explicitly specified (usually textually) somewhere, as parts of the picture are moved, these relationships might change. Pictures specified via exact or computed locations are difficult to specify in a visual editor. Though iteration can be represented (textually) via ellipses; recursion, loops and conditionals are difficult to represent in a visual framework.

On the other hand, it is often difficult to visualize the graphical structure implied by a textual description. This necessitates a tedious run-display-edit cycle to get the required layout. Another problem is that exact positional values are always required, even when the user does not care about the exact placement. Positioning visual elements to provide an aesthetically pleasing picture are difficult to produce via textual languages.

The solution to this dichotomy, of course, is to provide a system that integrates both textual and graphical modes for manipulating and describing the design. Much work has been carried out in this area. The Tpack module generation system [56] takes the approach of using graphical editors to create small pieces of geometry called *tiles* and using a procedural language to lay out and connect these tiles. DPL [57] and Sam [58] show the user both the graphical and textual view of the design being constructed and allow the independent editing of each. If the graphical view is edited, the textual view changes appropriately and vice versa. Tweedle [59] deals with general graphics and takes a similar approach but extends it by allowing the textual language to be procedural and incremental. A less desirable though still useful approach is taken by Henderson's functional geometry system [36] in which the graphical display is generated from a textual description. Any editing has to be carried out on the textual description. The graphics cannot be directly edited. This is essentially the same approach taken in the  $\mu$ FP and  $\nu$ FP systems. All of the layouts in this dissertation are generated directly from  $\nu$ FP descriptions.

#### 1.7 Overview

This research describes a method based on applicative languages [60] for the specification, evaluation and synthesis of hardware algorithms. Though this dissertation explores the role of applicative languages can play throughout the design spectrum—from specification down to implementation—it mainly concentrates on the synthesis of space and time domain hardware implementations of algorithms. This method is supported by a set of tools that is being developed at the University of California at Los Angeles. The goal of this effort is to provide designers with an environment in which they can rapidly explore various alternative designs for their algorithms. Thus, it is possible to specify the algorithm at any arbitrary level of abstraction and have the system rapidly evaluate performance parameters (e.g., speed, area) so that designers can make informed decisions during the synthesis process. The advantage

of using an applicative language is that it ties together the specification of the algorithm, the synthesis of the circuit and the evaluation of the implementation.

νFP, the system described here, is based on using a strict<sup>4</sup>, applicative-order<sup>5</sup> functional language to represent combinational and sequential behavior. Others have explored incorporating applicative languages into VLSI design and have shown them to be viable. Lahti [61] used an applicative language to describe various combinational hardware structures. Johnson [62] utilized a non-strict, normal-order<sup>6</sup> applicative language to describe and synthesize sequential digital circuits. Cardelli and Plotkin [63] take a formal approach to describing sequential circuits with an emphasis on verification. Meshkinpour [64] and Sheeran [65] extended Backus' FP language with operators to handle sequential circuits. ELLA [12], SILAGE [11], and LUSTRE [49] are applicative design languages which have been used to describe sequential hardware structures.

$\nu \mathcal{FP}$  uses a transformational approach to synthesis. A representation at one level of abstraction is converted into a representation at a lower level of abstraction using pre-defined substitutions<sup>7</sup>. These substitutions have been previously proved to preserve the meaning of the representation. Hence the final implementation is guaranteed to behave the same as the specification. Others have used a transformational approach in the design of VLSI systolic arrays [66, 67]. In these approaches delays are added and removed according to transformation rules in such a way that the output function remains invariant. Transformation approaches have to be supplied with an initial solution.

There are other methods [68] for the synthesis of circuits. Most use some form of a labeled graph with nodes as cells or functions, and edges as communication lines or precedence relations [69, 70, 71, 51]. This graph is then mapped into an implementation by scheduling and allocation. Allocation is mapping the data flow graph into hardware modules and data paths between these modules [72, 73]. Scheduling is the mapping of the control nodes to particular instances of time. Formal approaches of synthesizing behavioral descriptions into implementations in space-time are shown in [74, 75].

This dissertation highlights the impact of applicative languages in the design process from specification to implementation. Chapter 2 provides an introduction to the  $\nu \mathcal{FP}$  system and some of its features.  $\nu \mathcal{FP}$  is a strict, applicative-order functional language. The role of applicative languages in the specification of algorithms is explored in the next chapter. Chapter 4

<sup>&</sup>lt;sup>4</sup>A function is said to be strict if and only if its value is undefined when any of its arguments is undefined.

<sup>&</sup>lt;sup>5</sup>In applicative-order evaluation the arguments to a function are evaluated before the function application is performed.

<sup>&</sup>lt;sup>6</sup>In normal-order evaluation, the leftmost outermost reducible expression is evaluated first. Hence functional applications are carried out before the arguments to the function are evaluated.

<sup>&</sup>lt;sup>7</sup>Transformations that replace a function name by its definition will be called substitutions.

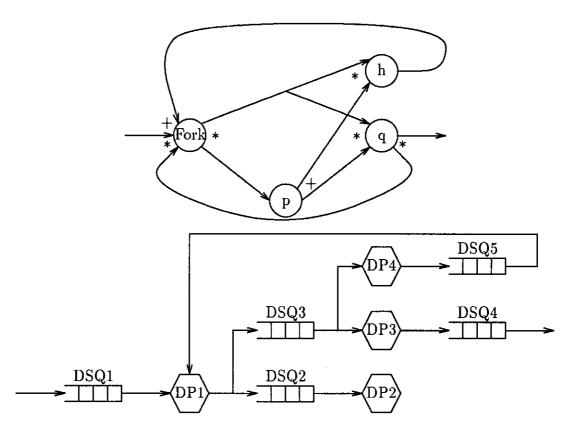

discusses how applicative languages (and the  $\nu \mathcal{FP}$  system in particular) are helpful in evaluating various alternative designs that may be constructed from the same specification. In order to explore the effects of using an applicative language in abstraction and refinement during design,  $\nu \mathcal{FP}$  was proposed as the interpretation domain language for the Graph Model of Behavior (GMB) in the SARA system. Chapter 5 describes how  $\nu \mathcal{FP}$  allows provable refinements in the GMB and how it can be used to prove equivalences between different views of the same representation.

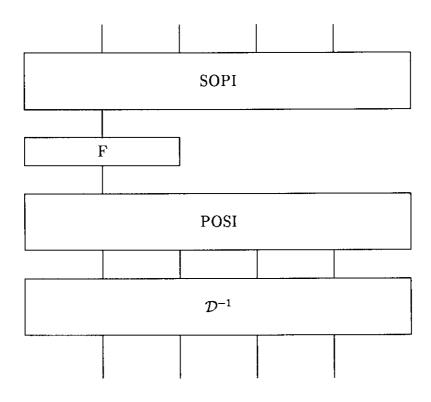

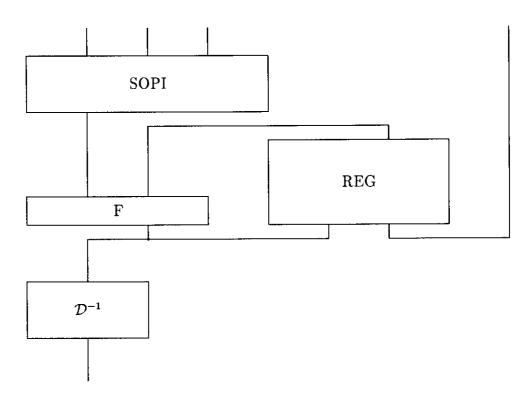

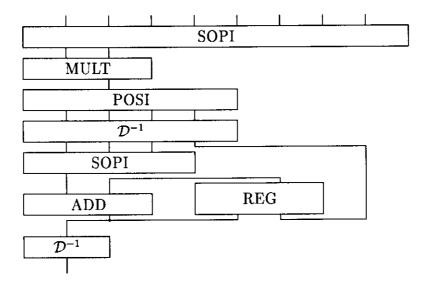

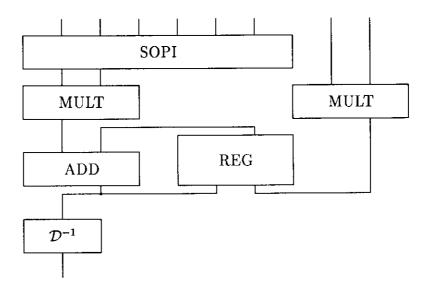

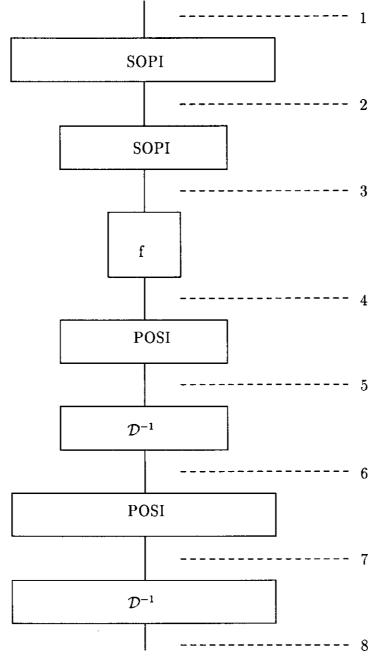

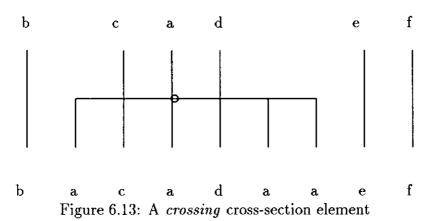

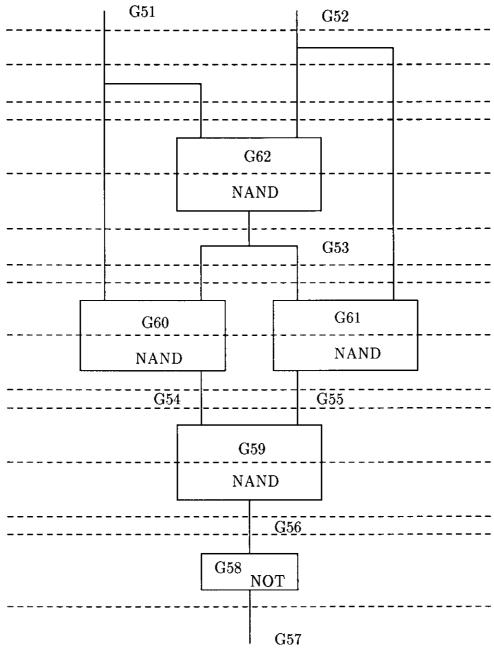

The transformation of an algorithm in the abstract to an implementation in space-time is described in chapter 6. The  $\nu \mathcal{FP}$  synthesis process proceeds as follows. First the specification is prepared. Then various high-level designs are carried out and evaluated with respect to performance criteria. The design process continues using refinement until primitives are reached. The design is evaluated at each stage to make sure it will meet the goals. At this point, the layout of the circuit can begin. The first step is to lay out the algorithm in space (section 6.3). If this meets the design goals, the synthesis is over. If this approach takes too much space, time synthesis may be attempted. This is covered in section 6.4. When the synthesis is complete, the internal representation is converted into a form acceptable to lower level layout tools for final fabrication. This is the subject of section 6.6. Sheeran's  $\mu FP$  [65] is the system that is closest to the one proposed in this dissertation. Chapter 7 discusses the differences between the two systems and points out the tradeoffs involved. The dissertation concludes with a description of the contributions of this work and suggestions for future explorations. Appendix A provides a complete and precise definition of the  $\nu \mathcal{FP}$  language. Appendix B clarifies some aspects of GMB semantics.

# Chapter 2

# The $\nu \mathcal{FP}$ System

This chapter gives an overview of the  $\nu \mathcal{FP}$  language and the  $\nu \mathcal{FP}$  system that includes language processors and evaluators.

#### 2.1 Brief Introduction to $\nu \mathcal{FP}$

$\nu\mathcal{FP}$  extends the language FP [60] proposed by Backus with additional functional forms and primitives. In contrast to  $\mu$ FP [65], which extends FP's semantics to operate on streams, the semantics of  $\nu\mathcal{FP}$  are the same as those of FP when it is used to specify algorithms. A program in  $\nu\mathcal{FP}$  (as in FP) is an expression, corresponding to a function, that maps objects into objects. Objects are either atomic (numbers or strings) or sequences of objects. The distinguished atom  $\perp$  denotes an undefined value. By definition, any sequence which contains  $\perp$  as an element is itself undefined and thus equal to  $\perp$ . This is another way of saying that  $\nu\mathcal{FP}$ , like FP, has strict semantics. This means that if any argument to a function is undefined, the result of evaluating the function is also undefined. Formally,

$$\forall f, f: \bot \equiv \bot. \tag{2.1}$$

The strictness property allows functions to be defined as total functions over all inputs and implies that  $\bot$  is in the domain of every function. Other applicative languages have non-strict (sometimes also called lazy) semantics. There are advantages and disadvantages of each approach. Having strict semantics is particularly helpful in a distributed environment because if an error develops in any particular part of the program, it is guaranteed that the error will propagate everywhere and eventually the whole program will terminate. On the other hand,

arithmetic functions

$$\begin{array}{c} +: \langle 1,5 \rangle \rightarrow 6 \\ & *: \langle 3,2 \rangle \rightarrow 6 \\ \\ \text{logical functions} \\ & \text{andg}: \langle 1,0 \rangle \rightarrow 0 \\ & \text{nandg}: \langle 1,0 \rangle \rightarrow 1 \\ & \text{org}: \langle 0,0 \rangle \rightarrow 0 \\ & \text{xorg}: \langle 1,1 \rangle \rightarrow 0 \\ \\ \text{predicates} \\ & \text{atom}: \langle 1,2 \rangle \rightarrow \text{false} \\ & =: \langle 3,3 \rangle \rightarrow \text{true} \\ \\ \text{selector functions} \\ & 3: \langle 2,\langle 4,5 \rangle, 6,\langle 8,\langle 9,10 \rangle \rangle \rangle \rightarrow 6 \\ & \text{last}: \langle 1,4,6 \rangle \rightarrow 6 \\ \end{array}$$

Table 2.1: Primitive Functions

strict semantics prohibit the use of incomplete (and possibly infinite) data structures which can be useful in some computations.

The primitive functions of  $\nu \mathcal{FP}$  consist of arithmetic, logical, predicate and selector functions, examples of which are shown in table 2.1. The cases involving an argument of  $\bot$  (equation 2.1) are omitted from the definitions for brevity. Examples of primitive structure modifying functions are shown in table 2.2. Functional forms are used to combine primitive functions into more complex functions. Some example functional forms are shown in table 2.3. A complete description of the  $\nu \mathcal{FP}$  primitives and forms is found in appendix A.

A major syntactic difference between  $\nu \mathcal{FP}$  and Backus' FP is that parameters to functions may be named and then referred to in the function body with restrictions similar to those specified in Backus' extended definitions [76] for FP. As with Backus' extended definitions, it is understood that the parameter names do not refer to input *objects*, but rather to the functions that create the particular input objects.

```

\begin{array}{lll} \operatorname{trans}: \langle \langle 1,2,3\rangle, \langle 4,5,6\rangle \rangle & \rightarrow \langle \langle 1,4\rangle, \langle 2,5\rangle, \langle 3,6\rangle \rangle \\ \operatorname{apnd1}: \langle 1,\langle 2,3,4\rangle \rangle & \rightarrow \langle 1,2,3,4\rangle \\ \operatorname{apndr}: \langle \langle 1,2,3\rangle,4\rangle & \rightarrow \langle 1,2,3,4\rangle \\ \operatorname{dist1}: \langle x,\langle a,b,c\rangle \rangle & \rightarrow \langle \langle x,a\rangle, \langle x,b\rangle, \langle x,c\rangle \rangle \\ \operatorname{distr}: \langle \langle a,b,c\rangle,x\rangle & \rightarrow \langle \langle a,x\rangle, \langle b,x\rangle, \langle c,x\rangle \rangle \\ \operatorname{iota}: n & \rightarrow \langle 1,2,\ldots,n\rangle \\ \operatorname{pick}: \langle k,\langle x_1,\ldots,x_n\rangle \rangle & \rightarrow x_k \text{ if } k \leq n \\ \operatorname{null}: x & \rightarrow (x=\langle\rangle \Longrightarrow \operatorname{true}; \operatorname{false}) \end{array}

```

Table 2.2: Structural Primitives

```

compose

(f \circ g) : x \longrightarrow f : (g : x)

construct

[f,g,h]:x \longrightarrow \langle f:x,g:x,h:x \rangle

applytoall

& f:\langle p,q,r\rangle \rightarrow \langle f:p,f:q,f:r\rangle

constant

%k:x

\rightarrow k \text{ if } x \text{ is not } \perp

rightinsert

!f:\langle x_1,\ldots,x_n\rangle\to f:\langle x_1,!f:\langle x_2,\ldots,x_n\rangle\rangle

treeinsert

sequential

\operatorname{\mathsf{seq}} f: \langle x_1, \dots, x_n \rangle \to \operatorname{\mathsf{apndr}}^{\, \circ} \left[ \operatorname{\mathsf{seq}} f: \langle x_1, \dots, x_{n-2}, 1 \circ y \rangle, 2 \circ y \right]

where y = f : \langle x_{n-1}, x_n \rangle

map

\{f_1, f_2, \ldots, f_n\} : \langle x_1, \ldots, x_n \rangle \rightarrow \langle f_1 : x_1, f_2 : x_2, \ldots, f_n : x_n \rangle

```

Table 2.3: Functional Forms

A  $\nu \mathcal{FP}$  definition like

is exactly equivalent to the FP extended definition

$$\underline{xdef} f \circ [x, y] = \dots$$

There are two restrictions on which functions can be defined with parameters. The first is that, as in Backus' extended definition, the body of the function must be distributive with respect to the parameters. Formally, a  $\nu \mathcal{FP}$  expression E is distributive with respect to the variables  $v_1, v_2, \ldots, v_n$  if and only if

$$E(v_1, v_2, \ldots, v_n) \circ h \equiv E(v_1 \circ h, v_2 \circ h, \ldots, v_n \circ h)$$

For example,

defun

$$f$$

( x , y )

$$[q \circ x, r \circ y]$$

enddef

is distributive, but

defun

$$g$$

( x , y ) [  $p$  ,  $q \circ x$  ,  $r \circ y$  ] enddef

and

are not. The second restriction, which is not present in Backus' extended definition, is that the parameter names must be simple and distinct. That is, a function like

defun

$$k$$

(x, x)

+  $\circ$  [x, %3]

enddef

is not allowed. In other words, unlike Backus' extended definitions, there is no pattern matching allowed in the parameters. Under these restrictions, it is very easy to convert a definition with parameters into one without parameters. The conversion process consists of replacing each occurrence of a parameter in the body by the corresponding selector function. For example, function f above could be converted to

```

FullAdder =

[org ° [org ° [andg ° [1,2],andg ° [2,3]],andg ° [1,3]],

xorg ° [1,xorg ° [2,3]]]

```

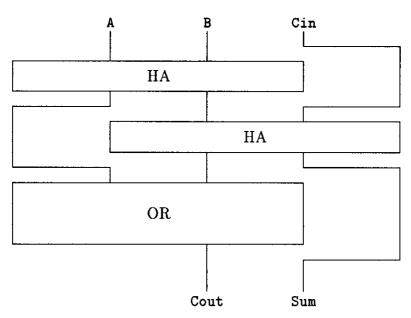

Figure 2.1: A Full Adder in Backus' FP

```

defun FullAdder(a,b,Cin)

[((a andg b) org (b andg Cin)) org (a andg Cin),

a xorg (b xorg Cin)]

enddef

```

Figure 2.2: A Full Adder in  $\nu \mathcal{FP}$