### Computer Science Department Technical Report University of California Los Angeles, CA 90024-1596

**COMMUNICATIONS ON VLSI**

Frank Andre Schaffa

July 1990 CSD-900019

### UNIVERSITY OF CALIFORNIA

### Los Angeles

### Communications on VLSI

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy in Computer Science

by

Frank Andre Schaffa

| ·<br>· |   |   |   |  |

|--------|---|---|---|--|

|        | * |   |   |  |

|        |   |   |   |  |

|        |   | • |   |  |

|        |   |   | · |  |

|        |   |   |   |  |

|        |   |   |   |  |

|        |   |   |   |  |

|        |   |   |   |  |

© Copyright by

Frank Andre Schaffa

1989

The dissertation of Frank Andre Schaffa is approved.

Gerald Estrin

Sank Rennels

Dave A. Rennels

Bennet Lientz

Bruce Rothschild

Mario Gerla, Committee Chair

University of California, Los Angeles

1989

In memory of my grandmother Klara

To my wife Vera

To my parents Alfred and Ellen

To my brothers Ralph, Thomas, and Ronald

| : |  |  |

|---|--|--|

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

iv

| • |  |  |  |

|---|--|--|--|

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

# Contents

| 1 | Int | roduction                                           | 1   |

|---|-----|-----------------------------------------------------|-----|

|   | 1.1 | Motivation                                          | 1   |

|   | 1.2 | Related Works                                       | 2   |

|   | 1.3 | Contributions and Organization of this Dissertation |     |

| 2 | Int | erconnection and Delay                              | 5   |

|   | 2.1 | Introduction                                        | 5   |

|   | 2.2 | Components                                          | 6   |

|   |     | 2.2.1 Scaling                                       | 8   |

|   | 2.3 | Area and Interconnection                            | 10  |

|   | 2.4 | Delay                                               | 11  |

|   |     | 9.4.1 Daining C.1                                   | 11  |

|   |     | 9.4.9 D 1/                                          | 13  |

|   |     | 9.4.9 To 1 1 2 miles 1                              | 15  |

|   | 2.5 | Conclusions                                         | 18  |

| 3 | Net | work Choices for VLSI                               | 20  |

| _ |     | •                                                   | 20  |

|   | 3.1 | Introduction                                        | 20  |

|   | 3.2 | Taxonomy                                            | • • |

|   | 3.3 | Performance Criteria                       | 22         |

|---|-----|--------------------------------------------|------------|

|   | 3.4 | Design Criteria                            | 23         |

|   | 3.5 | Critique of some Topologies for VLSI       | <u>?</u> 4 |

|   |     | 3.5.1 Discussion of Solutions              | 25         |

|   | 3.6 | "Appropriate" Networks for VLSI            | ?7         |

| 4 | VL! | SI Networking Approach 2                   | 9          |

|   | 4.1 | Introduction                               | 29         |

|   | 4.2 | Motivation                                 | 29         |

|   | 4.3 | Networking                                 | 31         |

|   | 4.4 | Differences from Conventional Environments | }2         |

| 5 | The | e Grid/RingNet Solution Approach 3         | 4          |

|   | 5.1 | GridNet                                    | }4         |

|   |     | 5.1.1 Topology                             | 14         |

|   |     | 5.1.2 Protocol                             | 15         |

|   |     | 5.1.3 Results - GridNet                    | 18         |

|   | 5.2 | GridNet/p2 - A Different Protocol          | ŀ2         |

|   |     | 5.2.1 Protocol                             | ŀ3         |

|   |     | 5.2.2 Results                              | ļ5         |

|   | 5.3 | RingNet                                    | Į9         |

|   |     | 5.3.1 $2in - 2out$ Topologies              | Į9         |

|   |     | 5.3.2 Protocols for Slotted Rings          | 52         |

|   |     | 5.3.3 Protocols for RingNet                | 66         |

|   |     | 5.3.4 Results                              | 70         |

|   | 5.4 | Conclusions                                | 72         |

| 6   | Ro              | uting                                | 75 |  |  |

|-----|-----------------|--------------------------------------|----|--|--|

|     | 6.1             | Our Domain                           | 75 |  |  |

|     | 6.2             | Routing Mechanisms                   | 76 |  |  |

|     |                 | 6.2.1 Broadcasting                   | 80 |  |  |

|     | 6.3             | The Routing Problem                  | 82 |  |  |

|     | 6.4             | Routing Algorithm                    | 83 |  |  |

|     | 6.5             | Applying the Results                 | 85 |  |  |

|     | 6.6             | Routing Assignment by Flow Deviation | 87 |  |  |

|     | 6.7             | Comparing the Algorithms             |    |  |  |

|     | 6.8             | Conclusions                          | 91 |  |  |

| 7   | Con             | clusions                             |    |  |  |

|     |                 |                                      | 92 |  |  |

|     | 7.1             | Summary of Results                   | 92 |  |  |

|     | 7.2             | Extensions of this Work              | 93 |  |  |

| Bil | Bibliography 96 |                                      |    |  |  |

# List of Figures

| 2.1 | Geometry of Interconnection                    | (  |

|-----|------------------------------------------------|----|

| 2.2 | Geometry of a MOS Transistor                   | 7  |

| 2.3 | Interconnection Scaling                        | ç  |

| 2.4 | RC Model                                       |    |

| 2.5 | Driving Schemes                                | 14 |

| 2.6 | Delay versus Distance                          | 15 |

| 2.7 | Zoning of a Interconnection Wire               | 16 |

| 2.8 | Throughput and Delay versus Number of Segments | 17 |

| 2.9 | G versus Number of Segments                    | 18 |

| 3.1 | Topologies Classification                      | 22 |

| 3.2 | Dont of the Natural Maria 1 and 1              | 27 |

| 4.1 |                                                | 20 |

| 4.2 |                                                | 30 |

| 1.2 | The Scaling of the Hierarchy of a VLSI Chip    | 31 |

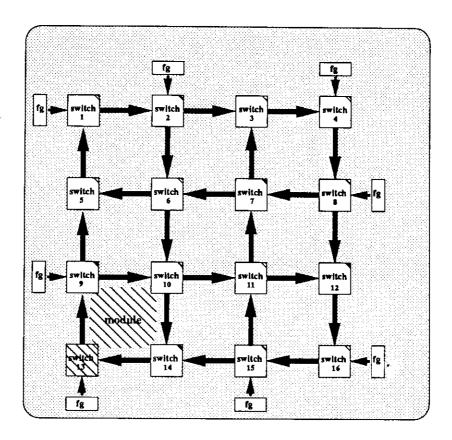

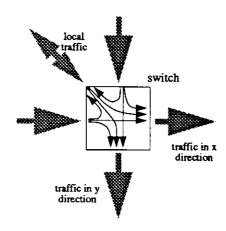

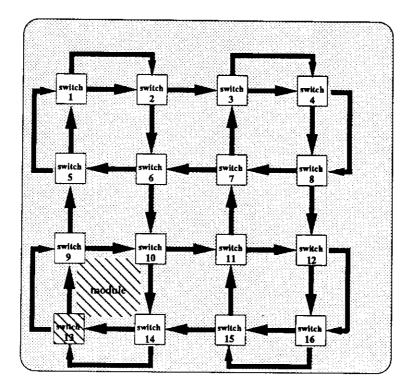

| 5.1 | GridNet                                        | 35 |

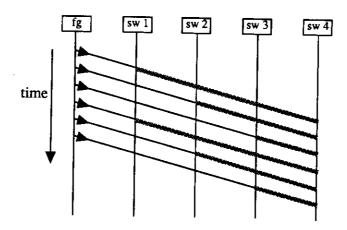

| 5.2 | Timing of Frames                               | 36 |

| 5.3 | Frame Generator                                | 36 |

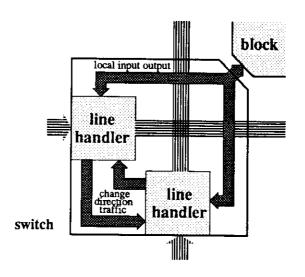

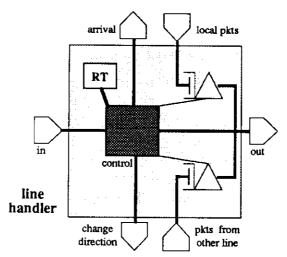

| 5.4 | The Switch                                     | 37 |

| 5.5 | The Line Handler                               | 37 |

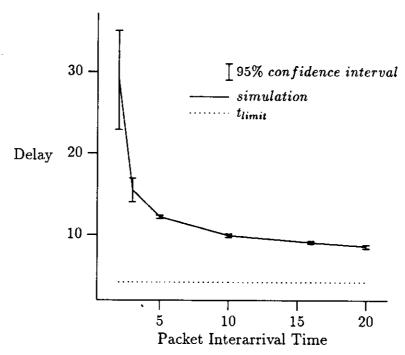

| 5.6  | Delay versus Arrival Time for GridNet                      | 39 |

|------|------------------------------------------------------------|----|

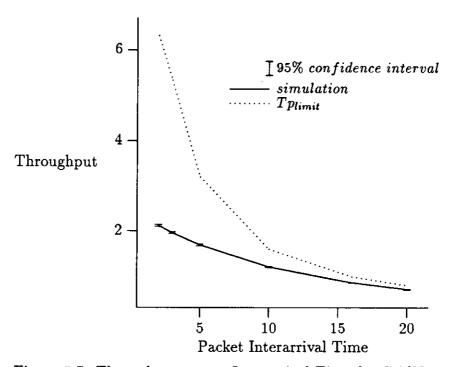

| 5.7  | Throughput versus Interarrival Time for GridNet            | 39 |

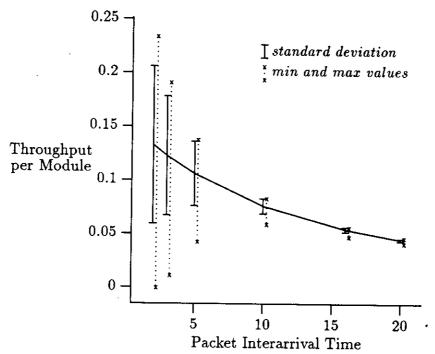

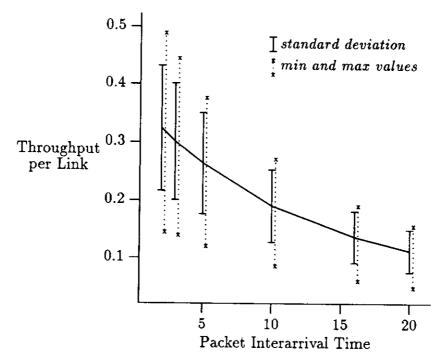

| 5.8  | Throughput per Module versus Interarrival Time for GridNet | 40 |

| 5.9  | Throughput per Link versus Interarrival Time for GridNet   | 40 |

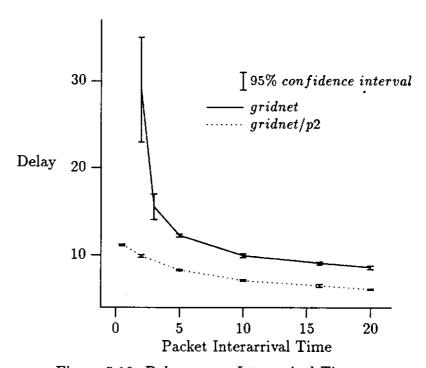

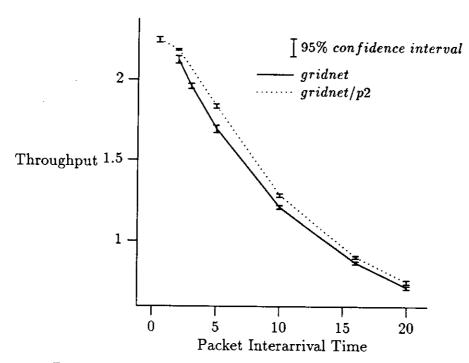

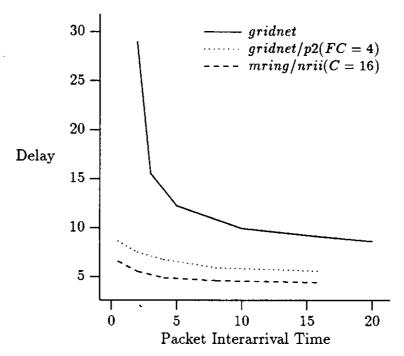

| 5.10 | Delay versus Interarrival Time                             | 45 |

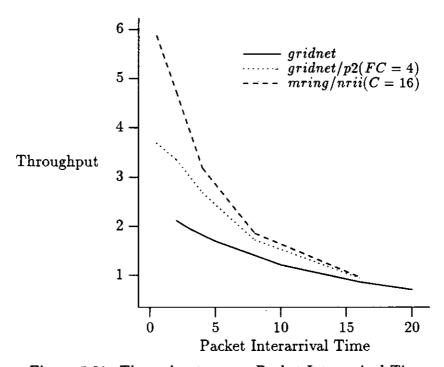

| 5.11 | Throughput versus Interarrival Time                        | 46 |

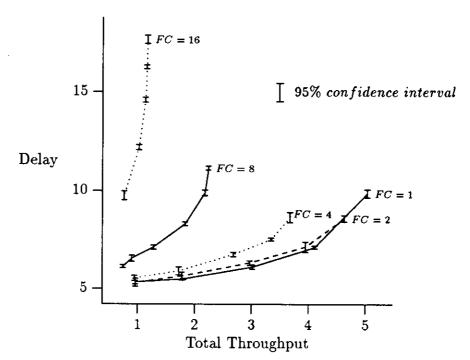

| 5.12 | Delay versus Throughput                                    | 47 |

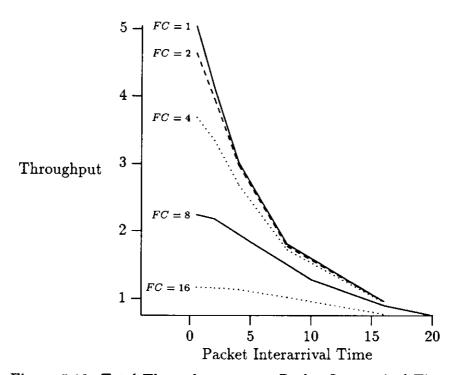

| 5.13 | Total Throughput versus Packet Interarrival Time           | 47 |

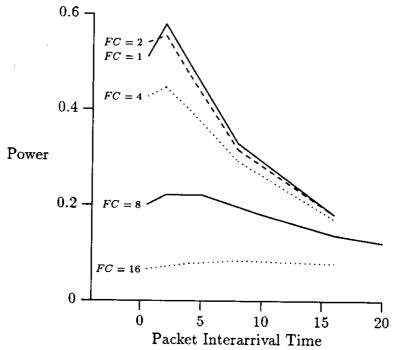

| 5.14 | Power versus Packet Interarrival Time                      | 48 |

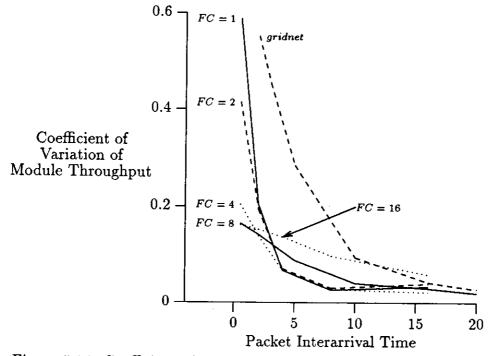

| 5.15 | Coefficient of Variation versus Packet Interarrival Time   | 48 |

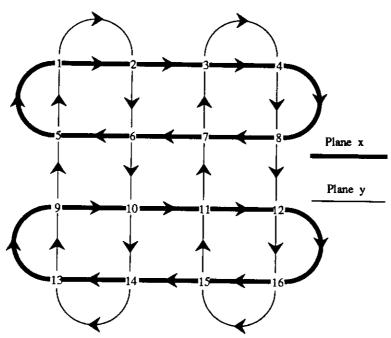

| 5.16 | MRing Topology                                             | 50 |

| 5.17 | DRing Topology                                             | 51 |

| 5.18 | Cubic Topology                                             | 52 |

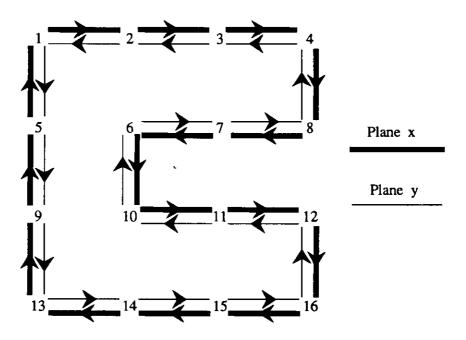

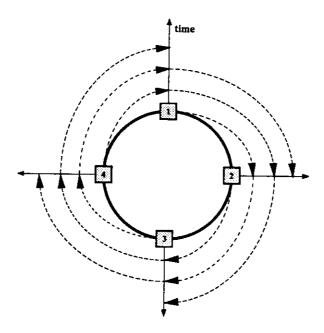

| 5.19 | Cyclic Topology and Flow                                   | 54 |

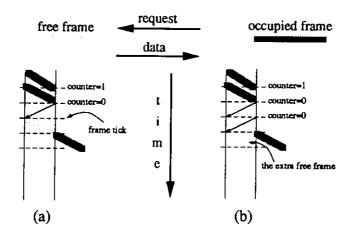

| 5.20 | Timing and Flow of Data and Control                        | 54 |

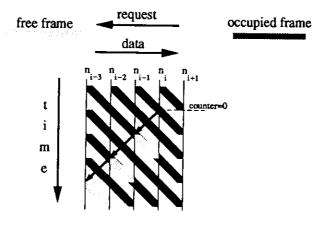

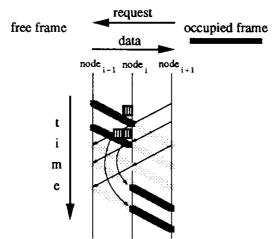

| 5.21 | Flow of Free Frame Requests                                | 56 |

| 5.22 | One Buffer Only                                            | 57 |

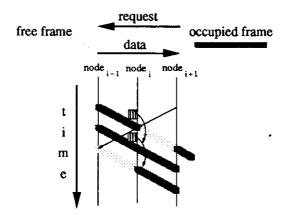

| 5.23 | Progression of Packets in a Lock Step Case                 | 60 |

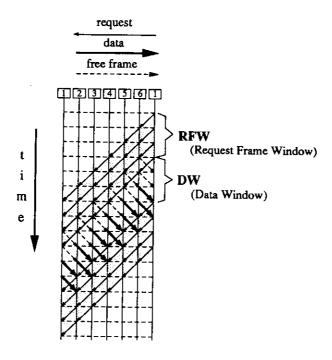

| 5.24 | RFW and DW Windows                                         | 62 |

| 5.25 | Two Buffers Only                                           | 63 |

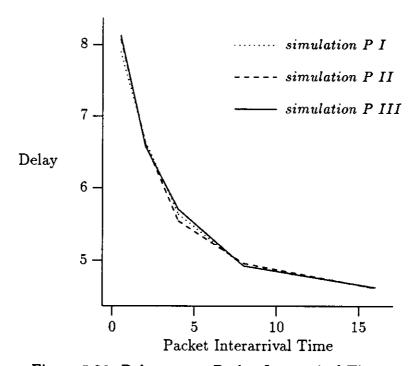

| 5.26 | Delay versus Packet Interarrival Time                      | 65 |

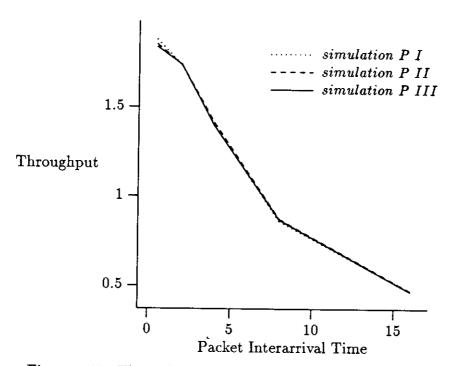

| 5.27 | Throughput versus Packet Interarrival Time                 | 66 |

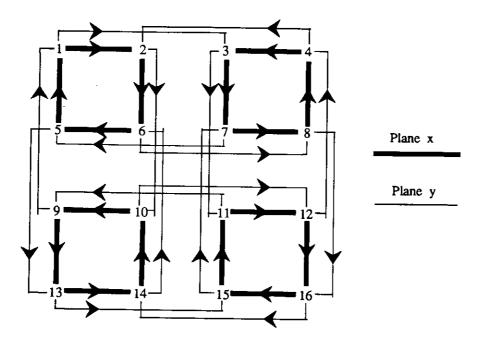

| 5.28 | Flow of Data in a Switch                                   | 67 |

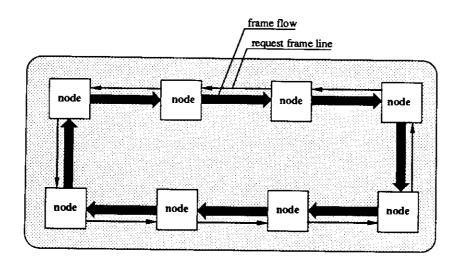

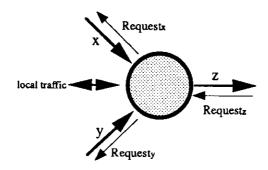

| 5.29 | Node Traffic Flow                                          | 69 |

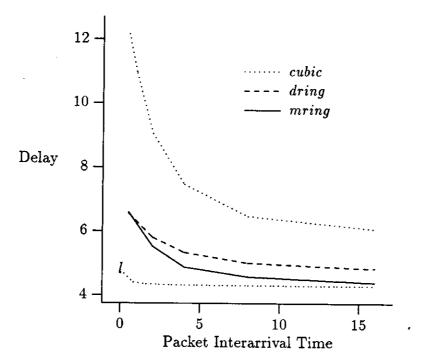

| 5.30 | Delay versus Packet Interarrival Time                      | 71 |

| 5.31 | Throughput versus Packet Interarrival Time                           | 71 |

|------|----------------------------------------------------------------------|----|

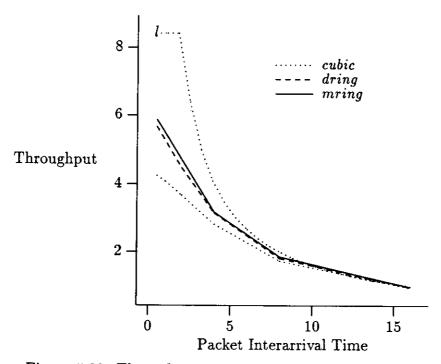

| 5.32 | 2 Delay versus Packet Interarrival Time                              | 72 |

|      | 3 Throughput versus Packet Interarrival Time                         |    |

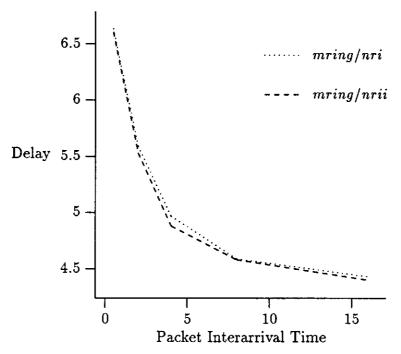

|      | Delay versus Packet Interarrival Time                                |    |

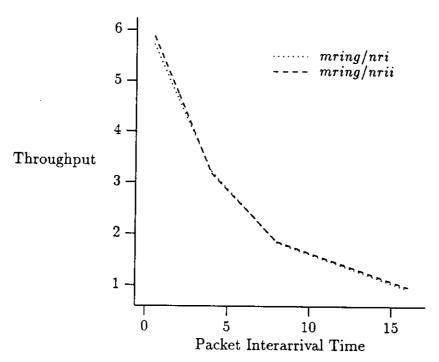

| 5.35 | Throughput versus Packet Interarrival Time                           | 74 |

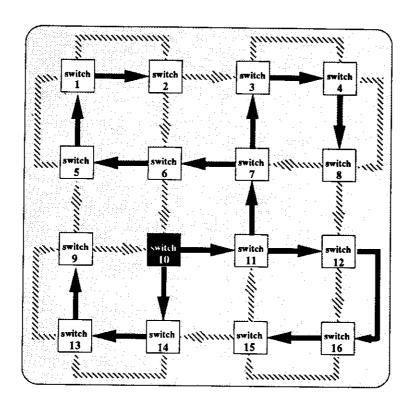

| 6.1  | Network Topology                                                     | 76 |

| 6.2  | Deflection Routing                                                   | 77 |

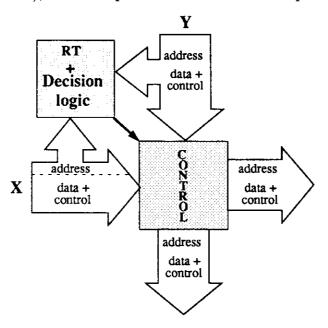

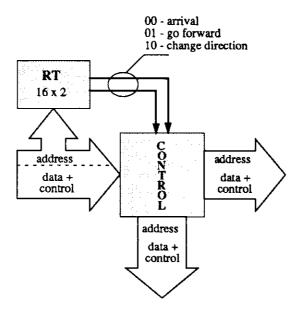

| 6.3  | Routing with Table-Lookup (RT)                                       |    |

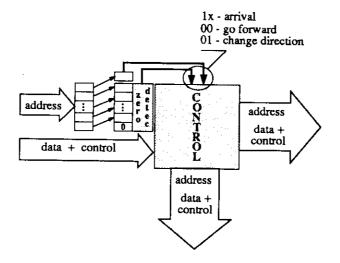

| 6.4  | Routing with Shift and Decide (SD)                                   |    |

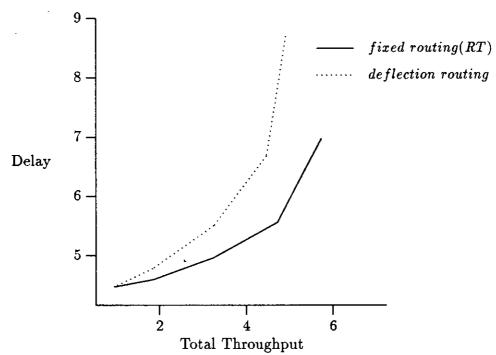

| 6.5  | Comparison Between Fixed and Deflection Routing                      |    |

| 6.6  | Broadcast Originating from switch <sub>10</sub>                      |    |

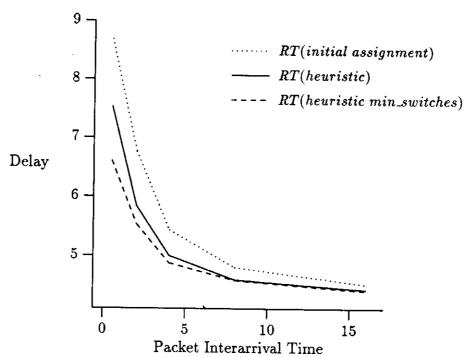

| 6.7  | Total Delay versus Interarrival Time for Initial and Optimal RT      | 86 |

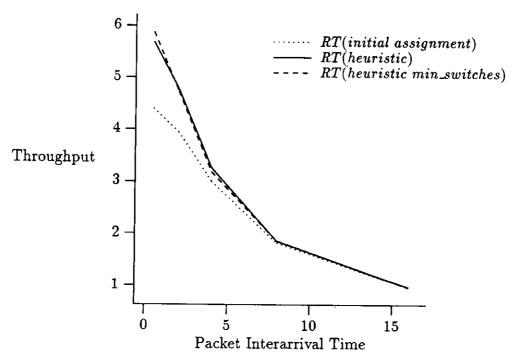

| 6.8  | Total Throughput versus Interarrival Time for Initial and Optimal RT | 86 |

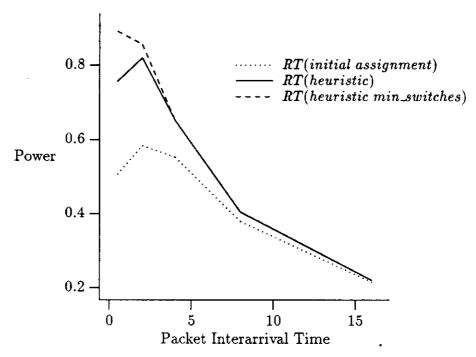

| 6.9  | Power versus Interarrival Time                                       | 87 |

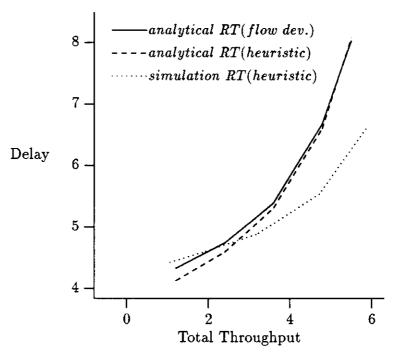

| 6.10 | Total Time versus Total Throughput for Uniform Load                  | 89 |

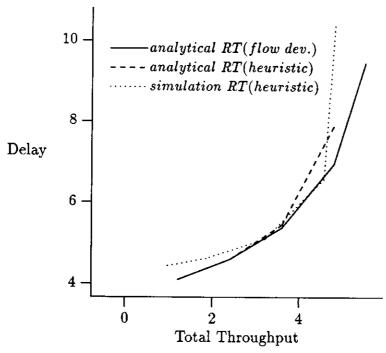

|      | Total Time versus Total Throughput for Non Uniform Load              | 00 |

xii

# List of Tables

| 2.1 | MOS Device Scaling                                                    | 8  |

|-----|-----------------------------------------------------------------------|----|

| 2.2 | Interconnection Scaling                                               | ç  |

| 2.3 | State of the Art Technology Evolution                                 | 10 |

| 3.1 | Time Comparison Between Unidirectional and Half-Duplex Links .        | 27 |

| 5.1 | Aggregated Link Utilization Efficiency                                | 49 |

| 5.2 | Decision Logic on $Plane_x$                                           | 67 |

| 6.1 | Decision Logic for Output Links                                       | 78 |

| 6.2 | Table Entries for Broadcast Originating from switch <sub>10</sub>     | 81 |

| 6.3 | Distribution of Alternative Minpaths Between Source-Destination Pairs | 84 |

#### ACKNOWLEDGMENTS

The Ph.D. process is long and depends on the help and involvement of many people. I am very thankful to those who have helped me along the way.

First of all, I would like to thank my advisor and friend Mario Gerla for his support in those difficult moments and for always being there when I needed him. He was patient and forthcoming with directions and suggestions for improvements to my research. I am also thankful for the other committee members, Gerald Estrin, Dave Rennels, Bennet Lientz, and Bruce Rothschild.

During my stay at UCLA, I have made friends for life, thus fulfilling needs other than academic ones. I would like to thank my brazilian friends, Edmundo, Valmir, Rolim, Nagib, and Suruagy, other fellow students, Jaime, Miquel, Ravi, Dorab, Paul, Marc, Hector, and Leon. I thank Dick Muntz for many interesting and in depth discussions on many different subjects. Verra Morgan has been an increadible friend, that I so often depended on. I thank Doris Sublette for her helpful and positive attitude. Finally I thank the dissertation group for many lively discussions on this subject matter.

I am also grateful to the CAD-LAB folk that provided me with many hours of cpu time to run my RESQ simulations and experiments.

This work was partially supported by a fellowship from CAPES, from the Ministry of Education, Brazil. I am very thankful to them for making it possible for me to come to UCLA for the Ph.D. program.

Finally I would like to thank my parents, brothers, and especially my wife Vera for her encouragement, support, and for being so proud of my achievements.

### **VITA**

| January 15, 1955 | Born in Sao Paulo, Brazil                                                                              |  |

|------------------|--------------------------------------------------------------------------------------------------------|--|

| 1977             | Engenheiro Eletricista<br>Escola Politecnica da USP, Sao Paulo, Brazil                                 |  |

| 1979–1980        | Teaching Assistant  Escola Politecnica da USP, Sao Paulo, Brazil University of California, Los Angeles |  |

| 1980             | Masters of Science in Computer Science<br>Escola Politecnica da USP, Sao Paulo, Brazil                 |  |

| 1981–1985        | CAPES/Brazil Fellowship                                                                                |  |

| 1982–1989        | Post Graduate Research Engineer<br>University of California, Los Angeles                               |  |

### PUBLICATIONS AND PRESENTATIONS

- 1. F. Schaffa and L. Moscato, "A Distributed Architecture Machine: Recovery through Reconfiguration," Fifteenth International Symposium on Mini and Microcomputers, April 1981.

- 2. F. Schaffa, "Reconfiguration on a Distributed Architecture Machine," EPUSP Master's Thesis, November 1980.

### ABSTRACT OF THE DISSERTATION

#### Communications on VLSI

by

Frank Andre Schaffa

Doctor of Philosophy in Computer Science

University of California, Los Angeles, 1989

Professor Mario Gerla, Chair

As technology continues to evolve, we have reached a point where the internal interconnection in VLSI requires a more careful analysis due to the increasing delay of the interconnection in relation to gate delays. In the foreseeable future, the impact of cross chip communication will become increasingly more critical on the performance of integrated systems and the way they are designed.

In this work we propose an approach called RingNet, which is based on strategies that minimize the interconnection delay and at the same time increase the total throughput. RingNet is specifically tailored to the given design constraints, which are quite different from conventional network constraints. Various versions of the RingNet protocols are discussed in terms of different characteristics such as liveness, flow control, fairness, and buffer requirements. Results based on simulation are presented. These protocols have no central control, e.g., the access mechanism is distributed with inherent flow control.

An important issue in the performance of a network is how information is routed from source to destination. We develop a heuristic algorithm which achieves good results when compared with optimal mathematical programming solutions. We also developed approximate analytic solutions which we compare with simulation results.

The results obtained in this work can be extended to high speed packet switching networks, that integrate voice, video and data communication. The thrust is the use of streamlined protocols with low overhead to achieve low packets delay and overall high throughput.

# Chapter 1

## Introduction

### 1.1 Motivation

In the foreseeable future, because of the advances of technology and the continuous evolvement of VLSI, we will be confronted by a new design paradigm as the performance bottleneck continues to shift from gate delay to interconnection delay. Therefore, we are reaching a point where the internal interconnection requires a more careful analysis and new directions for its design have to be sought.

The basic function of interconnection is to carry information between the processing elements of a system. Interconnection can be observed from the lowest level where it is just a piece of conducting material to a higher level where it encompasses a whole complex system. At the lowest level, wires connect gates, which are the lowest "processing" elements. The higher level, on chip, deals with the interconnection of modules and keeps evolving with the developing technology. The major impact of this new design paradigm will be reflected on the higher levels of the interconnection hierarchy.

Two major issues concerning interconnection in VLSI are 1) the cost in area [Sei84] and 2) the cost of propagation delay [YT84]. Interconnection is known to employ a great deal of area, which is a major resource. Interconnection competes with how much functionality can be integrated. The other issue, dealing with propagation delay of signals in the interconnection on chip is mainly caused by stray capacitance and resistance.

We will show that we can achieve some definite benefits in terms of interconnection sharing. Sharing can save area; however, this is only achieved by implementing some higher level of functionality, for instance, routing and destination checking. This is accomplished by additional logic that also takes area and power. There-

fore, for a given communication scheme (protocol, routing, node interconnection) area can be saved if compared with a point to point non-shared interconnection. As a result, this "saved area" can be used for increased integration of functions or for redundancy, which may increase reliability. Moreover, regarding reliability, the existence of a network makes it easier to functionally replace a non-working module.

### 1.2 Related Works

Another motivation for this work is the difficulty of implementing large clocked systems [FK85]. The reason is the inevitable problem of clock skews and delays, which can be especially acute in VLSI systems as they become larger and denser. The paper [FK85] shows that on two-dimension arrays, which is the case for VLSI, it is impossible to run a clock such that the maximum clock skew between two communicating modules will be bounded by a constant as the system grows, and therefore an asynchronous scheme is proposed. They also made some experimental trials from which they concluded that an equipotential clock distribution was many times slower than a pipelined one.

Anceau [Anc82] presents a synchronous solution based on a distributed system organization, where each module has its own fast clock (each module is within a small isochronic region). It communicates with the other modules also synchronously via a bus, however at a slow clock speed. Metastability problems are avoided by preserving the clocks in phase. The obvious drawback of this approach is the slow communication capability because of the speed of the bus and the contention for this single slow broadcast bus. This result reinforces our proposed system framework of independent modules that are interconnected to others via a network with the objective of optimizing throughput and minimizing delay. The network operates independently of the modules. This distinct functionality assists the hierarchical design approach, which is specially desirable in VLSI.

Mazumder in [Maz87] presents an interesting evaluation of three types of static interconnection for VLSI with the criteria of three orthogonal aspects: physical (chip area and dissipation), computational speed (message delay and message density), and cost (chip yield, operational reliability, and layout cost). The three topologies considered were: binary tree, cube connected cycles and two dimension meshes. The choice of these topologies was motivated by their wide interest in the literature, for their optimal VLSI layout in terms of the  $AT^2$  metric [Tho80], and because they belong to different classes.

The results are based on O(N), where N is the number of "processors". The problem with this approach is that N for a VLSI chip is rather small, between 16

and 64 and therefore O(N) results can be misleading, because constant and other factors are not taken into account. In reference to the computational aspects, the average message delay is based on the average message path length. The problem is that this in only true if there is no contention for the links, hence this is an optimistic lower bound for the delay. The average message density [Maz87], define as  $\frac{N\cdot D}{L}$  (where N is the number of processors, D is the average path length, and L is the total number links), can provide some guidance in terms of bottlenecks, however it is important to keep in mind that this is very dependent on the traffic pattern, which is not considered there.

Seitz [Sei84] discusses the topologies for concurrent VLSI architecture in very general terms based mostly on the algorithm communication requirements without going into the merits of VLSI constraints.

Tewksbury [TH88] describes a sparsely connected mesh network for a large number of cells (modules) (N > 400) for a massive parallel multicomputer. However, while this approach might be interesting for WSI and wafer to wafer systems, we believe it is not practical for VLSI due to the large amount of resources needed just for the interconnection.

### 1.3 Contributions and Organization of this Dissertation

In Chapter 2, we start by analyzing a simplified model which describes the behavior of signals transmitted on long distance wires. This model is based on results taken from the existing literature and provides us with a better understanding of the delay performance due to stray capacitances and resistances. It also gives us the opportunity to observe how future technology, and its scaling down of component sizes, will affect the interconnection. Based on this model, different driving schemes for long distance interconnection are evaluated. The scheme that provides the best results is based on providing enough current to charge/discharge the stray capacitance, and segmenting the wire with buffers, so that the wire resistance does not limit the charging/discharging current. An interesting property results from the segmentation, namely, the "pipelining" effect that occurs since buffers isolate one segment from the other. Hence, different information may reside in the line as it is being piped through, effectively increasing the throughput. These two factors, lower delay and the pipelining effect, motivate us to search for a networking solution for the long distance communication problem on chip.

Our objective in Chapter 3 is to place the VLSI interconnection network in the general framework of interconnection networks. We start by presenting a taxon-

omy, followed by performance criteria for VLSI. We also discuss other important design criteria related to the VLSI arena, for instance, layout restrictions and number of ports per node. Common topologies are analyzed and appropriate design decisions are discussed based on the taxonomy.

In Chapter 4, based on the list of candidates and the design criteria presented in the previous chapter, we look further into the specific requirements and characteristics of an on-chip network that is appropriate for the general VLSI design framework. We find that the most cost effective approach is a hierarchical design approach. The most significant advantage of this approach is the separation of the communication "details" from the modules, namely, computation, which may facilitate resource sharing, logical reconfiguration, reduce the pin count, and others. Considerations on the implementation lead us to assume a network characterized by a small number of switches, streamlined protocols, and small packet size (word wide, bit long). We also discuss the advantage of using unidirectional links.

Our major contribution is detailed in Chapter 5 where we present different topologies and protocols to implement the network on chip. We discuss mesh topologies (Gridnet) and ring topologies (RingNet). A variety of protocols suitable for these topologies are described and analyzed in terms of different characteristics such as liveness, flow control, fairness, and buffer needs. Results based on simulation are presented.

Another important issue which impacts network performance, is the routing of information from source to destination. In Chapter 6, we present different routing schemes: adaptive (based on deflection) and; static (source routing as well as destination routing). We also develop an algorithm based on heuristics to find static routing tables for a given traffic pattern. The algorithm achieved good results when compared with optimal solutions. The latter were obtained by routing assignment employing the flow deviation method. A side benefit of the optimal routing model is to provide throughput and delay estimates which can be compared with simulation results.

In chapter 7 we summarize our research accomplishments and point to different directions in which this work may be extended.

# Chapter 2

# Interconnection and Delay

### 2.1 Introduction

In this chapter, we will discuss one important problem that afflicts interconnections in VLSI design and is becoming more prevalent as technology advances: the time delay of signals transmitted over the interconnection. The "real estate" area required by the interconnection is also important and will be briefly discussed.

The technological advancements in integrated circuit design has scaled down the minimum feature size, thus increasing the number of devices that can be integrated in a given area. At the same time, it has scaled up the size of the chip that can be produced with reasonable yields. The main benefit is that more functionality can be integrated; however, this does not happen without some cost, as we shall see.

The ultimate number of devices that can be integrated in a chip is limited not only by feature size, but also by the area taken up by interconnection. Studies in the published literature [Sei84, MRRS84, Gam81, HMD78] show that as more functionality is integrated, the greater is the area devoted to the interconnection of functional modules.

In terms of time behavior, the scaling down of the feature size will shift the dominant contribution of delay from the device itself to the long distance interconnections (across the chip) [GMS87, BM85, SM82].

We first present the fundamental components of VLSI that are related to performance. Following, we discuss the scaling effects on components, on interconnection, and on the area for interconnection. Next, we study the time behavior of signals over metal wires and signal driving schemes for long wires. Finally, we discuss some tradeoffs between delay and throughput.

This will serve as the basis for our networking proposal. The study presented here will be the underlying work from which we will develop the framework that will motivate the integration of a network on chip.

### 2.2 Components

Integrated circuits (MOS technology) are created by the superposition of different layers of conducting and insulating materials on top of a substrate. The proper placement of these layers will create the transistors (the active elements) and their interconnection. Each layer has resistance and capacitance; inductance will be assumed negligible. The characteristics of these elements determine the performance of the system.

The interconnection is also built as a conducting layer separated by insulation. Hence, interconnection lines have resistance as well as capacitance. Above certain dimensions, the interconnection may have a great impact in performance, since the current driving capacity of the active devices is quite limited (because of size). The electric current determines how fast the total capacitance is charged and/or discharged for a change in the signal applied to the lines.

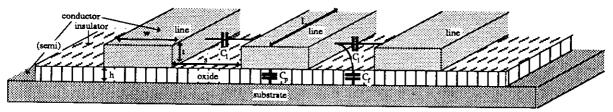

Figure 2.1: Geometry of Interconnection

We present now the electrical characteristics of the basic components:

• (a) wires - The geometry of an interconnection wire can be seen in Figure 2.1. The resistance of an interconnection (by unit length) can be expressed as:

$$R_I = \rho \frac{1}{wt} \tag{2.1}$$

where  $\rho$  is the resistivity of the conductor ( $\rho = 2.7\mu\Omega \cdot cm\ Al$ ),  $w\ t$  are respectively the width and the thickness of the interconnection.

The accurate evaluation of capacitance of the interconnection requires very time consuming calculations. Sakurai [Sak83] developed some simple formulas for wiring capacitance whose accuracy is within a few percent of more complex models. These results have been confirmed by [NDN87].

For our use, these approximations are quite acceptable. These results have also been used in other papers, for instance [BM84]. The capacitance per unit length includes the plate capacitance, the coupling capacitance between adjacent lines, and also the fringe capacitance. The expression for  $C_i$  per unit length is:

$$\frac{C_I}{E_{ox}} = 1.15(\frac{w}{h}) + 2.80(\frac{t}{h})^{0.222} + 2[0.003(\frac{w}{h}) + 0.83(\frac{t}{h}) - 0.07(\frac{t}{h})^{0.222}](\frac{s}{h})^{-1.34}$$

(2.2)

where  $E_{ox}$  is the dielectric constant for silicon oxide  $(3.9 \cdot 8.85 \cdot 10^{-14} F/m)$ , h is the thickness of the oxide under the metal plate, s is the distance between adjacent metal lines, t and w are the thickness and the width respectively of the metal line. (Refer to Figure 2.1).

The first two terms in the expression are the dominant factors reflecting "area" and "fringe" capacitance. The other terms account for neighboring lines effect. Smith [SPP87] shows that the influence of added neighboring lines, for number of pairs  $\geq 2$  is rather small, and that the difference between one pair to two pairs is also quite small. This makes the 3 lines on ground plane model by Sakuray even more attractive.

• (b) transistors - Although transistors are non linear devices, we will apply a simple model that is used throughout the literature. [WE85, Muk85]

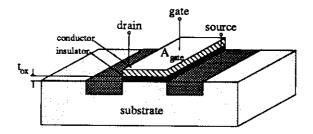

Figure 2.2: Geometry of a MOS Transistor

For capacitance,

$$C_{tr} = \frac{E_{ox}}{t_{ox}} \cdot A_{gate}$$

where  $E_{ox}$  is the permittivity of silicon oxide,  $t_{ox}$  is the the oxide thickness, and  $A_{gate}$  is the area of the gate.

For resistance,

$$R_{tr} = R_{\square} \cdot \frac{L}{W}, \quad R_{\square} = \left[\mu \frac{E_{ox}}{t_{ox}} (V_{gs} - V_{th})\right]^{-1},$$

where  $\mu$  is the mobility of electrons in the channel ( $m^2/V \cdot s$ ),  $V_{gs}$  is the gate source voltage,  $V_{th}$  is the threshold voltage, and L W are related to the dimensions of the gate, length and width respectively. The equation models the resistance on the linear region. In the light of this analysis, this is conservative, since  $R_{tr}$  in saturation is lower than in the linear region and transistors operate in both regions, hence, the effective resistance becomes lower. This implies that the resistance of a long interconnecting wire becomes even more relevant, as will see in the delay section.

### 2.2.1 Scaling

The advances in the VLSI process technology have led to smaller dimension devices and at the same time, to larger available area for circuit integration. In order to understand how these advances will impact circuit design, a scaling theory was developed. A first-order MOS scaling model was introduced by Dennard et al. [DGY+74] and it is used throughout the literature [MC80] [WE85]. Basically it applies a dimensionless factor  $\alpha$  ( $\alpha > 1$ ) to all dimensions, voltages, and concentration densities. Table 2.1 presents the scaling effects. This particular table is from [WE85].

|        | Parameter                     | Scaling Factor (alpha) |

|--------|-------------------------------|------------------------|

| Device | Length $L_c$                  | $1/\alpha$             |

|        | Width $W_c$                   | $1/\alpha$             |

| 1      | Gate oxide thickness $t_{ox}$ | $1/\alpha$             |

|        | Supply voltage $V_{dd}$       | $1/\alpha$             |

| Result | Gate delay                    | $1/\alpha$             |

|        | Power dissipation             | $1/\alpha^2$           |

Table 2.1: MOS Device Scaling

Based on this first-order scaling theory for MOS technology, smaller dimensions imply faster transistors, i.e., switching delay scales down by  $\alpha$ , and the number of transistors on a same chip size scales up by  $\alpha^2$ . However, this only holds for small circuits. Performance of larger circuits is affected negatively by two factors: increased interconnection delay and increased interconnection area, the former using up area that could be used for logic.

Saraswat et al. [SM82] developed the MOS Scaling theory further to incorporate the effect of scaling on interconnection, classifying it in local interconnection and long distance interconnection. They take into consideration the scaling up of the usable chip area by a factor  $\gamma$  ( $\gamma > 1$ ).

| Parameter                                | Local Interconnection scale factor $\alpha$ | Long Distance Interconnection scale factor $\gamma$ |

|------------------------------------------|---------------------------------------------|-----------------------------------------------------|

| Interconnection distance Line resistance | $1/\alpha$                                  | γ                                                   |

| Line capacitance                         | $\frac{lpha}{1/lpha}$                       | $lpha^2\gamma$                                      |

| Line response                            | 1                                           | $\alpha^2 \gamma^2$                                 |

Table 2.2: Interconnection Scaling

The local interconnection scales down with  $\alpha$ , though its RC product remains constant, meaning that the time delay does not scale down. The time delay problem is even more critical regarding long distance interconnection: signals have to travel longer distances because of the scaling down of the devices and also because of the scaling up of the chip size. Furthermore, the smaller devices handle less power, which limits their current driving capability. Hence charging/discharging the interconnection takes longer. These two scaling effects can be seen in Table 2.2. Figure 2.3 illustrates the interconnection scaling.

For instance, line resistance for local interconnection is  $R = \frac{l}{w \cdot t}$  which implies in  $R_{\alpha} = \frac{l/\alpha}{w/\alpha \cdot t/\alpha} = R \cdot \alpha$ . For long distance,  $R = \frac{l}{w \cdot t}$  which implies in  $R_{\alpha\gamma} = \frac{l\gamma}{w/\alpha \cdot t/\alpha} = R \cdot \gamma \alpha^2$ . A similar development applies for line capacitance. Line response becomes the RC product.

Figure 2.3: Interconnection Scaling

The first order scaling is a simplified model of the advances of the technology. It is reasonably accurate and quite useful to provide insights into issues that arise with the changes in technology. The physical limit for the MOS technology is around minimum feature size of 0.1  $\mu m$ . Table 2.3 [Spe88] shows the advances regarding feature size and area. The results were obtained by simulation and

extrapolation of the limiting factors in the manufacturing process.

| Year | Minimum Feature Size | Area   |

|------|----------------------|--------|

|      | $\mu m$              | $mm^2$ |

| 1972 | 6                    | 10     |

| 1975 | 4                    | 15     |

| 1978 | 2.5                  | 24     |

| 1981 | 1.5                  | 40     |

| 1984 | 1                    | 60     |

| 1987 | 0.6                  | 100    |

| 1990 | 0.4                  | 150    |

| 1993 | 0.25                 | 240    |

| 1996 | 0.15                 | 400    |

| 1999 | 0.1                  | 600    |

Table 2.3: State of the Art Technology Evolution

## 2.3 Area and Interconnection

In VLSI, interconnection is known to be area intensive. Usually it takes up more than 50 percent of the total area. In [MRRS84] it is claimed that 60 to 80 percent of the chip area is taken for interconnection. Seitz in [Sei84] goes as far as claiming that interconnection takes usually 95 percent if taken at the transistor level, with 5 percent left to implement the transistors that effectively perform the computation. It is important to take this fact into account because it affects chip gate density and has two major consequences: less gates per chip because interconnection can be considered as an overhead in terms of area, and at the same time, larger distances between modules (functional blocks), affecting therefore, the performance since the increased distance implies increased delay.

Of course, interconnection cannot be avoided, since at the end it is what provides the communication internally and externally for the logic modules, which are the ones implementing the algorithms. This reinforces the notion that interconnection has to be designed carefully. The care is even more important for the upcoming technologies where interconnection will have a major impact on performance not only in area but also in time.

# 2.4 Delay

The effect of scaling in interconnection has been in focus in the literature over the past years. One of the most important results has been to show that interconnection delays will be of a major concern in the submicron technology arena [GMS87, NDN87, SPP87, BM85, SM82, MC80]. Scaling of interconnection per se was discussed in a previous section.

For the delay expression, we will use an approximate result by Sakurai [ST83]. This result is based on an exponential approximation. For the range of parameters we will be using, the relative error is claimed to be in the order of 1 percent.

Sakurai's result:

$$t = 1.02C_i \cdot R_i + 2.21(C_{tr} \cdot R_{tr} + C_{tr} \cdot R_i + R_{tr} \cdot C_i)$$

(2.3)

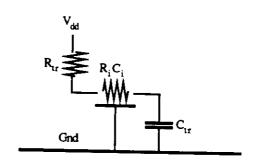

where  $C_i$  and  $R_i$  are the total capacitance and resistance of the interconnection, and  $C_{tr}$  and  $R_{tr}$  characterize the transistor. Figure 2.4 illustrate this.

Figure 2.4: RC Model

# 2.4.1 Driving Schemes

By looking closer at equation 2.3 we may ascertain how delay behaves in terms of the interconnection length l.

$$t(l) \sim C_I R_I l^2 + R_{tr} C_{tr} + (R_I C_{tr} + R_{tr} C_I) l$$

We note that the delay can vary from a constant (O(k)), to linear (O(l)),

to  $quadratic\ (O(l^2))$  behavior. We are considering metal interconnection where  $R_{tr}>>R_I.$

- O(k): when  $R_{tr}C_{tr}$  is the dominant factor. This is true for small l and for previous technologies where the interconnection did not play a significant role in delay (refer to Table 2.2).

- O(l): for certain ranges of l and technologies when the dominant factor is  $R_{tr}C_{l}l$

- $O(l^2)$ : at submicron technologies, the dominant factor becomes  $C_I R_I l^2$  as  $R_{tr} \leq R_I l$ .

Based on this, it was found that the delay could be kept at O(l) by breaking the line and buffering the signal (with so called repeaters) from space to space [GD85, WE85, Muk85, BM85]. By a similar reasoning in order to drive a high capacitance load, it should be driven by a series of drivers of incrementally larger size [HJ87, CPM86, GD85, BM85, Ram82, MR82].

With this in mind, we present and compare some different schemes for driving signals. We are only considering aluminum lines (metal wires) since we are interested in the lowest delay possible for long distance on chip. Other materials that are also used in interconnection like polysilicon and metal silicides have a considerably worse performance [SM82, Rei83] due to the high RC constant and are therefore used for very local interconnection. Similar study was done by Bakoglu [BM85].

The delay expressions for the driving schemes are based on expression 2.3 for each of the segments. We assume that the load on this network is equivalent to the gate of a minimum size transistor.

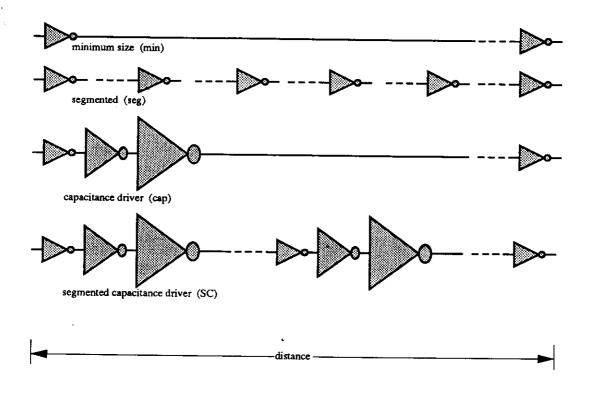

The driving schemes are (see Figure 2.5):

minimum size: A minimum size transistor driving the signal line.

$$t_{min} = R_i C_i + 2(R_{tr}C_{tr} + R_i C_{tr} + R_{tr}C_i)$$

segmented: In this case the line is segmented in equal size segments and each of them is driven by a minimum size transistor. These driver-segments are connected in series. The number of segments is such that it leads to a minimum delay regarding this scheme.

$$t_{seg} = \frac{R_i C_i}{k_s} + 2k_s (R_{tr} C_{tr} + \frac{R_i C_{tr}}{k_s} + \frac{R_{tr} C_i}{k_s}),$$

which is minimized by solving

$$\frac{\partial t_{seg}}{\partial k_s} = 0$$

hence,  $k_s = \sqrt{\frac{R_i C_i}{2R_{tr}C_{tr}}}$

capacitance driver: Since one of the major causes of the delay is the high capacitance of the lines, a scheme described in [MC80] is used. A series of drivers are cascaded in such a way that the next one is larger by a factor f, f > 1, therefore, more capable of driving current to charge/discharge capacitances. The number of drivers is optimal for the capacitance on the line. For ideal conditions, f = e [MC80]. When intrinsic delays are taken into account, 3 < f < 5 [HJ87].

$$t_{cap} = k_d f R_{tr} C_{tr} + R_i C_i + 2\left(\frac{R_{tr} C_{tr}}{k_d} + R_i C_{tr} + \frac{R_{tr} C_i}{k_d}\right)$$

with  $k_d = \ln\left(\frac{C_i + C_{tr}}{C_{tr}}\right) / \ln(f)$

SC driver: (segmented capacitance driver) A combination of the segmented and the capacitive driver to achieve the minimum delay.

$$t_{SC} = k_s k_d f R_{tr} C_{tr} + \frac{R_i C_i}{k_s} + 2k_s \left( \frac{R_{tr} C_{tr}}{k_d} + \frac{R_i C_{tr}}{k_s} + \frac{R_i r C_i}{k_s k_s} \right)$$

#### 2.4.2 Results

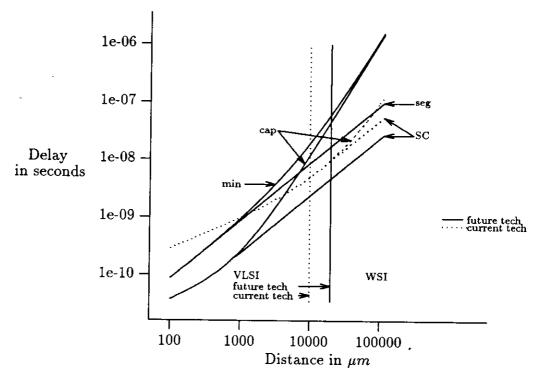

The results can be seen in Figure 2.6. The minimum size driver has the worst performance as expected. However, it is the one that consumes the least power and area.

The segment driver has a quasi-linear behavior: segments are added as distance grows when the delay of the line segment is comparable to the delay of the buffer. Otherwise, the delay would increase as the square of the line length because both, the resistance and the capacitance of the interconnection, increase linearly with the length, as it is the case with the min driver.

The capacitance driver has a significant improvement in the performance while the resistance of the interconnection is less than the driver resistance. From that point on, the RC of the line becomes the predominant factor and asymptotically this driver performs as the min driver.

The SC driver compensates for both, the capacitance and the resistance of the line. Segments are added as the resistance of the interconnection grows, and at

Figure 2.5: Driving Schemes

the same time, larger drivers are placed to adjust to the line capacitance. The values for  $k_d$  and  $k_s$  were found by numerical optimization. The split seen in the graph when compared to the capacitance driver occurs when the line starts to be segmented.

In Figure 2.6 we can observe an interesting fact regarding the relationship between the driving schemes and the technology stage: since for the current technology the split between  $t_{SC}$  and  $t_{cap}$  occurs beyond the diameter of the chip it means that the "bus solution" (so common in current designs) is a viable solution in terms of delay performance. However, for future technologies the results for low delay strongly suggest the use of segmentation, which is unidirectional by its nature, requiring a different approach to the chip communication problem. We also show in the figure, the accepted region for VLSI and WSI.

Furthermore, design decisions cannot only rest on these delay figures. In VLSI, equally important are the area and power needed for those different schemes when design decisions are being made.

An important point that hasn't been considered so far is the shape of the signal. After the signal passes through a long capacitive line, the transition from one voltage correspondent to a logical level to the other becomes slow due to

Figure 2.6: Delay versus Distance

low pass filtering characteristic of the line. These slow transitions increase the uncertainty of the logic level and more time is needed for the circuitry to decide, thus imposing more delay and possibly a metastable condition [MC80, GD85]. In this condition the level of the signal is such that it cannot reliably be interpreted as either high or low and, theoretically, it may remain in this state indefinitely. The regeneration of the signal helps to overcome this additional delay, as it is the case on the segmented lines where drivers are strategically placed. A piecewise analysis method which can be used to predict the logic propagation delays taking into account the finite slope of the input was developed by Bayruns [BJJF84].

## 2.4.3 Delay and Throughput

In previous works, the emphasis has been on the time delay that signals incur as they travel long distances in the chip [BM85, BM84, SM82, MR82, Ram82]. However, as important as it is to lower the delay, it is to increase the throughput, since both factors affect the transfer of information.

Therefore, it is not just a matter of how long it takes to send information from one point to another, but how much information can be sent at a given time.

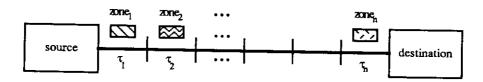

One of our conclusions in the last section was that dividing up the long distance

interconnection wire and buffering the signal at those points, effectively segmenting the wire, showed time behavior improvements. As a side effect, this also created "zones" of information, each zone corresponding to a segment. Because of the buffering, the segments become logically isolated, which implies that all zones may be carrying different information at a given time. As exemplified in Figure 2.7, the packets of information move from one zone to the next, from source to destination like in a pipeline. This is the property that we want to exploit in order to improve the throughput. We should also note, however, that the segmented interconnection becomes unidirectional since buffers have been inserted (as opposed to a continuous wire which electrically "broadcasts" the signals)

Figure 2.7: Zoning of a Interconnection Wire

In terms of throughput, the maximum throughput is the inverse of the highest segment delay. Trivially, one finds that the maximum throughput for a given distance, is for segments with equal delay, i.e., equally spaced buffers assuming same electrical characteristic for all segments and load capacitance at the end of the wire equivalent to the buffers.

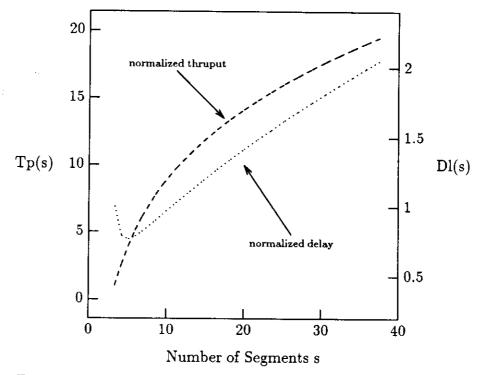

An interesting compromise can be accomplished between the end to end delay and the information throughput of an interconnection line. We define a benefit function G,

$$G(s,l) = \frac{Tp(s,l)/Tp(1,l)}{Dl(s,l)/Dl(1,l)}$$

where Tp(1,l) is the throughput over the interconnection with length l and with a single driver at the source. Tp(s,l) is the throughput for the interconnection with s segments. Dl(1,l) and Dl(s,l) are the analogous for end to end delay. Of course Tp(s,l) takes into consideration the pipelining effect.

G(s,l) is the proportional to throughput and inversely proportional to delay. Hence, the benefit is high when the end to end delay is small and the throughput is high. Optimizing G will lead to a good operating point of the system, e.g., a good compromise between delay and throughput. A concept analogous to benefit function G, known as "Power" [Gai83] was developed for computer networks. Power is defined as the ratio of Throughput over Delay. Again, power optimization leads to an effective operating point of a communication link.

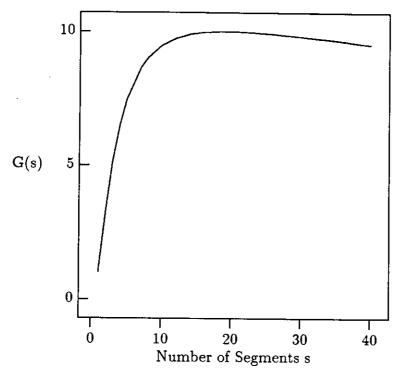

Figure 2.8: Throughput and Delay versus Number of Segments

The graph in Figure 2.8, shows the normalized throughput (Tp(s, l)/Tp(1, l))and the normalized delay (Dl(s,l)/Dl(1,l)) for varying number of segments s and for an interconnection with length l, where l is the typical VLSI diameter. The delay values were derived from the SC driver expression. The throughput is the inverse of the delay of a segment. As the number of segments increases, the delay decreases until the number of segments approaches the optimal number of buffers (as seen in the previous section). From that point on, the delay increases because of the added delay of the buffers. The graph in Figure 2.9 shows the functions Gversus s. We note that for a small number of segments, the benefit function G is low because the delay is high (less segments than the optimal number) and the throughput is low (small number of zones). As we increase the number of segments, we cross the point were the delay is minimum. If we continue to increase the number of segments, we will increase the throughput and the delay. This means that after some point, the benefit of the increased throughput will be offset by the increased delay. The reason for the increased delay is that for each added segment, the buffer delay accumulates to the total delay.

We observe that the sensitivity of G is high for a small number of segments. This implies that there is a high benefit even with a small number of segments. In terms of VLSI, this is interesting since more buffers mean more power dissipation and more occupied area and that a significant gain can be made with a small number of segments.

Figure 2.9: G versus Number of Segments

We should remark that  $G_{MAX}$  is not the absolute optimum for all applications, and that we should use the values for G as a guideline for the operating point regarding the compromise between throughput and delay.

## 2.5 Conclusions

In this chapter we have shown some of the trade-offs that will have to be considered when designing a long distance interconnection.

Moreover, the results obtained here strongly suggest that a communication solution for the upcoming technologies should be based on a slotted communication architecture so that low delay and high throughput can be attained. We envision the communication being broken down into different levels, each one with different characteristics. For example, three levels, the lowest being the point to point, the middle level using bus and the higher level utilizing some kind of network on chip.

Most of the VLSI chips built so far at the highest level have some kind of shared interconnection, mostly bus. This can be noticed in general purpose microprocessors, memories, dedicated processors, and many other designs.

We conclude by claiming that the interconnection of a VLSI chip should also be designed hierarchically and that at the uppermost layer, there should be a network that benefits from the segmentation of long lines and also profits from the pipeline effect introduced by the segmentation.

# Chapter 3

# Network Choices for VLSI

### 3.1 Introduction

The communication among the elements of a multiprocessing or multimodule system is the key to the exploitation of parallelism and performance. Interconnection networks is a wide field and a rich literature is available, presenting many different topologies, architectures, and implementations. It is not our aim to go into detail of these interconnection networks. The purpose of this chapter is to discuss topologies for VLSI adequate for the advancing technologies in the light of parameters presented in the previous chapter (Chapter 2), namely, delay, throughput, and area.

We first present a taxonomy for interconnection in order to have a framework for our discussion and will later complement it with issues that we consider important for VLSI. Further on, we will discuss different topologies under this framework.

## 3.2 Taxonomy

The taxonomy presented here is based on Feng's survey of networks [yF81]. His motivation was the essential points of a cost effective network from a practical point of view. We will use this as a starting point for our discussion on the intrachip VLSI network.

In selecting the architecture of an interconnection network, four design decisions are identified. They concern the operation mode, the control strategy, the switching method, and the network topology.

Operation mode: Communication is identified as synchronous for processing in which communication paths are established synchronously; and asynchronously in which connection requests are issued dynamically. Systems with both operations mode are also possible. Synchronous mode is used most in broadcast systems or small systems for data and/or instructions. Asynchronous communication is more suited for multiprocessing in which connection requests are issued dynamically.

Control strategy: Interconnection networks are typically made up of switching elements and their links. The interconnection functions are performed by properly setting the control of the switching element. This functions can be managed by a centralized controller - centralized control strategy - or by the individual switching elements in that case a distributed control strategy. This falls in the discussion of central or distributed control. Centralized control is usually simpler, however, failure and congestion are the negative side to it. On the other hand, distributed control is more complex in its design since issues like liveness, fairness have to be implemented.

Switching methodology: The two major switching methodologies are circuit switching and packet switching. In circuit switching, a physical path is actually established between a source and a destination. In packet switching, data is put into a packet and is routed throughout the network without establishing a physical connection path. In general, circuit switching is more suitable for bulk data transmission (large granularity), and packet switching is more efficient for short data messages (fine granularity) because of the set up time overhead compared to the address information in the packet. Combining the capabilities of both, circuit switching and packet switching, we identify integrated switching.

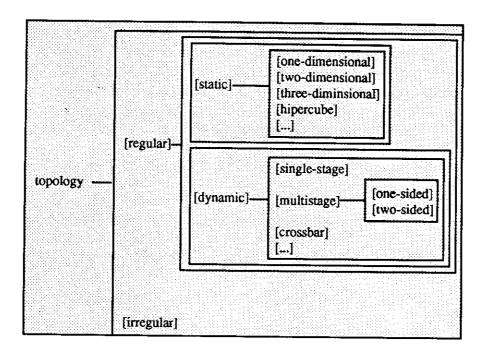

Network topology: A network topology can be represented by a graph where edges and nodes represent respectively the communication links and the switching points. Most of the topologies are regular and can be grouped in two categories: static and dynamic. The classification is depicted in Figure 3.1. For instance, ring is a regular static one-dimensional topology: links between two processors are passive and cannot be reconfigured to direct the connection to other processors. Dynamic topologies allow link reconfiguration by setting the network's active switching elements. A different way of looking at these categories is to verify how the interconnection itself is designed. If there is only one interconnecting layer between two nodes the topology is static and cannot be reconfigured (like a bus topology); on the other hand, if the interconnection layer consists of more then one layer, it can be reconfigured (like shuffle-exchange).

• The static topology category can be classified according to the number of dimensions in the connection space. Bus, linear array, are examples of one-dimensional static topology. Ring, star, tree, near-neighbor mesh, and

Figure 3.1: Topologies Classification

systolic arrays are two-dimensional. Three-dimensional topologies include chordal ring, 3-cube, and 3-cube-connected-cycle [PV81]. Furthermore, a d-dimensional w-wide hypercube contains w nodes in each dimension, and there is a connection to a node in each dimension.

• The dynamic topology has three different classes: single stage, multi-stage, and crossbar. Single stage network is composed of a stage of switching elements cascaded to a link connection pattern. The shuffle-exchange network is a single-stage network based on a perfect-shuffle connection cascaded to a stage of switching elements. Multi-stage network consists of more than one stage of switching elements and is usually capable of connecting an arbitrary input terminal to an arbitrary output terminal like benes, baseline, delta, omega, banyan networks [yF81, HLSM82, Fra81, CLYP81].

## 3.3 Performance Criteria

In order to select the appropriate design decisions presented in the previous section, we have to define a set of performance criteria and design parameters under which the network should operate.

Some common performance criteria are: delay, throughput, fairness, and cost. Delay is a measure of the time packets take to travel from origin to destination.

It may relate to the average time or to the maximum time. Throughput measures the number of packets that go across the network per unit time. Fairness refers to the equality of distribution of the bandwidth. Cost is related to the complexity and to the physical size of the design which determines its yield.

These criteria are not orthogonal, therefore, they conflict with one another. For instance, high throughput (desirable) may lead to high delay (undesirable) and low fairness (undesirable); low cost (desirable) by using serial communication may lead to high delay (undesirable).

Some of this conflicting issues may be assisted by strategies in order to meet the performance objectives:

- Routing mechanism: How packets are routed from source to destination. The mechanism helps to alleviate congestion by deviating packets to less used paths.

- Access protocol and flow-control: How packets get access to the network and how congestion is handled by slowing down the traffic coming to the network. By slowing down the traffic, delay decreases and fairness may improve.

- Redundancy: How redundancy and reconfiguration mechanisms may reduce manufacturing cost by increasing the yield or decreasing the maintenance cost by prolonging the useful life of the system.

## 3.4 Design Criteria

As important as the performance criteria for the network, are the design criteria (i.e. design variables and constraints) peculiar to VLSI design, which may determine how the performance criteria may be attained. Some of these issues are:

• Layout: Deals with how networks may be laid out on chip. There are a series of constraints since the basic space is a two dimensional one with a very limited number of independent layers that may overlap. The common value for these different layers is two or three. Some other important characteristics of this mapping are regularity, distance between switches, and the capacitance involved with this mapping. Care should be exercised to avoid complex layouts with wires crisscrossing; this would make it more prone to noise, crosstalk, greater capacitance, and also make it more difficulty for power distribution wires (power grid).

- Number of ports per switch: A large number of ports implies a more complex switch that needs more circuitry and consequently more area. This usually leads to slower switches with higher delay. Furthermore, more power would be needed for the extra load (logic and drivers), and an increased difficulty in the mapping, discussed above. Similar conclusion was reach by Fujimoto [Fuj83].

- Number of ports per bus: If a multiaccess, multiport bus is used, a larger number of ports involves higher capacitance on the bus since ports are capacitive loads. Hence, high driving currents are needed for faster transmission, implying larger drivers and larger dissipated power. The end result is an increase in delay through both, the driver chain and bus.

- Height and width of wires: Height and width of wires are parameters of the wire capacitance and resistance (see Chapter 2) and consequently parameters for the delay. However, the delay cannot go below some value because it is bounded by the maximum sectional current that may flow across metal lines. Currents above the limit produce metal migration [MC80, GMS87], which will literary carry metal away from the "hot spots" and eventually brake the connection. Using wider wires will increase the capacitance, which in turn will need more power (current). The height of the wire is limited by the technology. The "solution" lies in careful design.

# 3.5 Critique of some Topologies for VLSI

As we can see there is a wide range of interconnection network topologies, (see Figure 3.1), from the bus network at the lower bound to the crossbar at the upper bound of regular topologies. Neither are appropriate for highly parallel arrays [HLSM82]. The bus network is architecturally simple, but in an n-processor network only 1/n of the bandwidth is available for each processor. The crossbar network with every processor connected to all others, uses  $n^2$  switches to connect n processors. For VLSI, this structure becomes unfeasible because of the number of switches required and the layout complexity of interconnecting wires. Below we will discuss some of the most commonly proposed topologies for future VLSI technologies.

• Bus: Very regular and simple, however, there is a high penalty in delay for long distance and for the number of ports connected to it so that the transfer rates become quite limited. Also, since it is a unique shared resource, contention becomes high. This is the most commonly used intra-chip communication in current VLSI designs, though it will not be appropriate for

future technologies. However, a hierarchy of busses could be an appropriate solution for traffic patterns that hold physical locality.

- Ring: Because of the slotted nature of the optimal driving scheme for long distance interconnection (detailed in Chapter 2), ring offers a simple solution. With the use of an appropriate protocol, it is possible to have more than one active slot (a frame carrying data) at a time, and so a higher throughput may be achieved; however, delay is high (n/2). The layout can be easily accommodated for VLSI.

- Mesh: A regular mesh, with the placement of switches based on the optimal long distance driving scheme. A mesh-connected network is exemplified in [TH88].

- Trees: May have a good layout, the so called H tree [MA71, MR79], but non uniform distances may became a problem as well as routing, leading to low throughput and high delays and eventually to bottlenecks at the root (or close to the root). This topology is very sensitive to application.

- CCC: (Cube Connected Cycles) is an interesting arrangement, with high regularity and small number of ports. However, it does have non uniform interconnection length. From [PV81], length can be as high as half the chip size in the standard layout, to full chip size in the more economical layout. Hence, in spite of its nice placement, the delay through these long interconnections can greatly upset the performance of some algorithms.

- Hypercube (binary-cube): In a planar mapping of this topology (for a binary 6-cube see [Sei85]), the length of the links and the number of ports increases as dimensions grow. The layout is complex and costly in terms of area. Although routing seems simple, it can became quite hard when an optimal routing and flow control solution is sought.

- Omega nets and equivalents: Given that the delay is a function of the link length, the problem becomes the layout of the switches and the links among them. It is not possible to distribute the switches on a planar layout and connect them with equal link length (manhattan distance). Hence, this does not seems to be an appropriate solution for VLSI interconnection.

#### 3.5.1 Discussion of Solutions

The topologies presented, from the link point of view, fall in two categories: 1) point to point, 2) multiaccess.

The point to point fits very well with the results obtained on Chapter 2. At each point signals are amplified, the distances between the points can be such as to minimize delay, and the *zoning* allows for the pipeline effect, therefore higher throughput may be achieved.

The multiaccess should be a hierarchy of small busses so that the lengths of the busses are small and load (number of ports connected to it) is also small. By the virtue of the hierarchy, locality can be exploited by the applications which also improves the throughput. This ought to happen in a well designed system. (discussion in Chapter 1 - distribution of clock signals)

Links can be further classified as bidirectional or unidirectional. In multiaccess, busses are by their nature bidirectional, while in point to point, if we take into consideration the results of Chapter 2 (driving schemes), the suitable solution calls for unidirectional links.

In a mesh topology, switches are connected by point to point links which can be unidirectional or bidirectional. The major difference in terms of routing between uni and bidirectional, is that path lengths in the bidirectional case are, in most cases, lower.

In terms of implementation, in the bidirectional case, there are two possibilities: a single physical link that switches the direction of flow following some protocol (half-duplex) and a dual physical link, each link dedicated to one direction (full-duplex).

We will not consider the full-duplex solution because it is too expensive in terms of area for additional circuits and wires, besides the added complexity of the control circuit itself.

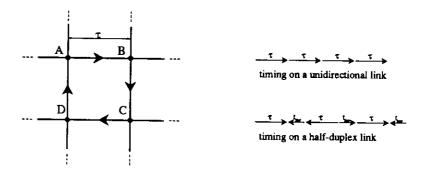

To compare the unidirectional and the half-duplex scheme, we refer to Figure 3.2 and Table 3.1. We assume that the system has a regular topology (mesh) for reasons discussed earlier and that it is slotted with time  $\tau$ , which is also the propagation plus circuit delay between adjacent switches. For the unidirectional case, links alternate direction in both orientations, vertical and horizontal. For the half-duplex,  $t_{sw}$  is the time it takes to switch direction. In Table 3.1, values in brackets are the worst case situations.

The last line of the table shows the average time under a uniform destination assumption. We notice that the lesser distance of the half-duplex scheme does not show a major delay reduction over the unidirectional scheme. Furthermore, if  $t_{sw} \geq \tau/4$ , the unidirectional scheme comes out the winner. One also finds that, as distance on the grid between source and destination increases, the difference in manhattan distance between the two schemes decreases.

Figure 3.2: Part of the Network Mesh and Timing

| from $\rightarrow$ to | unidirectional |                     | half-duplex               |                                                   |

|-----------------------|----------------|---------------------|---------------------------|---------------------------------------------------|

|                       | distance       | time                | $\operatorname{distance}$ | time                                              |

| $A \rightarrow B$     | 1              | $\tau$ [2 $\tau$ ]  | 1                         | $\tau \ [3\tau + 2t_{sw}]$                        |

| $A \rightarrow C$     | 2              | $2\tau$ [4 $\tau$ ] | 2                         | $\left[2\tau \left[6\tau + 4t_{sw}\right]\right]$ |

| $A \rightarrow D$     | 3              | $3\tau$ [6 $\tau$ ] | 1                         | $\tau \left[3\tau + 2t_{sw}\right]$               |

| average               | 3              | Τ                   | 8/3                       | $\tau + 4/3t_{sw}$                                |

Table 3.1: Time Comparison Between Unidirectional and Half-Duplex Links

In conclusion, we believe that the additional complexity of bidirectional links (half or full duplex) is too high a price to pay for the marginally shorter number of hops between node pairs, when compared to unidirectional links. Consequently, we will base our solution on the unidirectional scheme, which is simpler, needs less area and power and operates faster on a link basis.

# 3.6 "Appropriate" Networks for VLSI

Following Feng's design criteria, the space of possible network solutions is given by the cross product of the set of categories for each design decision. Applying the VLSI constraints discussed earlier, we obtain a subspace of solutions that we will explore further.

• Operation mode: should be asynchronous because of clock skew and clock distribution problems in VLSI [FK85] and delay issues discussed in Chapter 2.

- Control strategy: should be distributed based on the same reasons. A timely exchange of information in not possible.

- Switching methodology: for most applications packet switching seem more appropriate than circuit switching due to the nature of traffic, usually short messages. The problem with circuit switching would be the overhead of setting up the connections.

- Network topologies: based on the earlier discussion, mesh and ring seem the most appropriate for VLSI topology.

In order to come up with an appropriate and cost-effective interconnection switching network for a class of applications, compromises among basic characteristics must be reached.

# Chapter 4

# VLSI Networking Approach

#### 4.1 Introduction

In this chapter, we discuss the network approach to deal with interconnection at the highest level of the VLSI chips of future technologies.

We start by showing the hierarchy of interconnection at the present technology and how scaling affects it. We also present the advantages of the networking approach, the difference between the proposed scheme and other networks.

## 4.2 Motivation

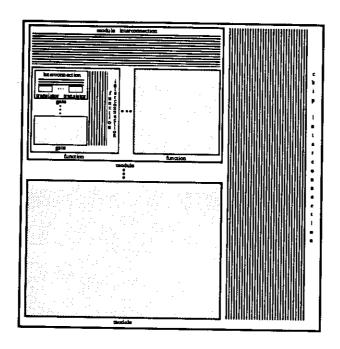

The hierarchical approach to VLSI design is a must due to the complexity involved [MC80, BK83, UKH85]; specifically, transistors are bundled into gates that in turn create functional blocks, which in turn are bundled into modules and so forth. At each increasing level on the hierarchy, more functionality is added. This is easily observed in practically all VLSI designs: microprocessors, memories, memory management units, floating point units, and many others.

The bundling is accomplished by the interconnection whose function is to transport signals from one transistor to another, from one gate to another, and so forth. The hierarchy that we see applied to the functional aspect, also applies to the interconnection, where each level has its own requirements. This is illustrated in Figure 4.1. Mead in [MR82] suggests that the number of wires must decrease exponentially as a function of their length, also implying that efficient designs must have a hierarchical structure.

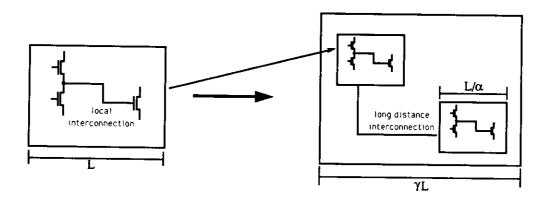

Figure 4.1: The Conceptual Hierarchy of VLSI Chip

In the current technology, the highest level of the hierarchy of intrachip interconnection is the interconnection of modules. The next level is outside the boundary of the integrated circuit. The module interconnection has so far been handled, in most cases, by point to point interconnection and by strategies based on bus. The bus communication strategies are very common and rely on a central model with tight control.

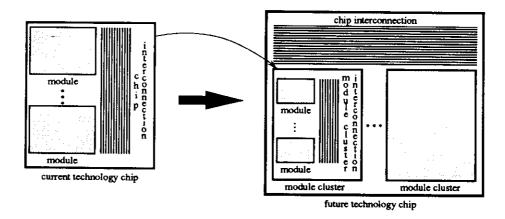

Given the technological advances presented in Chapter 2, we see the minimum feature size being scaled down (factor  $1/\alpha, \alpha > 1$ ), and chip size being scaled up (factor  $\gamma > 1$ ). Gate density is, hence increased and so is the available chip area. In this context, modules from the current technology, which were at the highest level of the on chip hierarchy will be bundled into module-clusters, and these clusters will become the next and last level on the on chip hierarchy. Figure 4.2 shows this.

To provide communication between these module-clusters we are proposing a networking scheme. We see networking on chip as a necessary step to keep up with the advances in technology. One of the motivations for the network framework is based on the delay results obtained on Chapter 2. In order to cope with the increasing line capacitance and resistance for long distance, and hence increasing delay, we observed that solutions should be based on reducing the length of the

Figure 4.2: The Scaling of the Hierarchy of a VLSI Chip

lines. Signals traveling long distances should have active elements properly placed on the interconnecting wire. Two benefits of this solution are: 1) delay does not grow as dramatically, and 2) the zoning effect that allows the coexistence of different information along the interconnection (pipelining). We will take advantage of both effects in our networking scheme.

One reason why networking has not yet happened in the current technology is because the interconnection delay problem presented in Chapter 2 is most significant for the developing technologies, that are still in experimental phase. The gain for todays technology, if any, would be small because of the tradeoff between the area for modules and the area for the intra-chip network. This will change, however, as gate density as well as chip area increases.

## 4.3 Networking

A strong point of networking is the development of an interface between the intercommunicating blocks. This interface creates the separation of the communication functions such as routing and flow control from the blocks themselves. There are many advantages for such a separation:

- better control over the complexity of design, since hierarchy is enforced,

- standard communication interface,

- communication decisions done on the network, relieving blocks from such functions,

- savings on area for interconnection (due to sharing communication channels),

- flexible addressing,

- combination of blocks that operate at different speeds.

The size of such a network is quite limited and is likely to vary from 16 to 64 nodes. Many tradeoff decisions have to be made to find out an appropriate number. Given that everything has to be integrated on a certain area, a balance between number of modules and their sizes has to be achieved. If the number of modules becomes too high, the overhead of the network in terms of area (for circuits and wires) and power needs become high and modules have a lower functional integration (they are smaller). In the opposite case, it might happen that modules become big and sluggish because of internal delays and network resources inadequate to support efficient communications. This will affect negatively the overall performance of the chip.

It is also important to point out that a network architecture providing full interconnection (as the one we propose) is not the ideal solution for all intra-chip communication situations. For specific architectures that can be categorized as systolic arrays [Kun82] other communication schemes will perform better. In that case communications usually occur only between neighbors, and there is no need for an effective and high performance global communication scheme, which is what we are aiming at.

# 4.4 Differences from Conventional Environments

The networks that we propose here are very different from conventional networks such as LANs or WANs. The goal of our networks is to achieve global high performance on intra-chip VLSI communication. Therefore, a very specialized set of requirements (different from conventional networks) must be taken into account. We envision these networks as characterized by:

- assured delivery,

- streamlined protocols,

- fast routing decisions,

- small packet size (one bit word wide),

- regular topology matching the two dimensions of integrated circuits.

To achieve the assured delivery we are assuming a perfect channel model. Once the subnetwork has accepted a packet, it can be assumed that it will arrive to its destination within a bounded time (no loss, no buffer overflow). Protocols should ensure that there is no buffer overflow. Loss due to failures is very unlikely, with probability smaller than the probability of failure of a module. (Recall that faults are a function of used area and switches are significantly smaller than modules [SAS83, KB84]). The motivation for such assumption is that it simplifies the design of the switches, making it feasible to implement them at this level of the hierarchy.

The protocols have to be simple and efficient since, in order to achieve the high performance, the logic decisions should be processed in the order of a few gate delays. Here the previous assumption of perfect channel comes very handy: no need for acknowledgement, time-out, and retransmission mechanisms. If those mechanisms were necessary, great amount of area would have to be dedicated. Besides, they would lower the response time of the protocol in two folds: circuits would be more complex and slower, and the protocol itself would have to dedicate bandwidth and processing time to handle them. Windowing mechanisms, common in other networks, are also prohibitively expensive it this domain. Obviously, there should be error checking of the transmissions. However, this should be at a higher level, such as process level, for example.

Routing of packets from source to destination, based on the same assumptions as the access protocol, has to be simple and efficient. The time frame magnitude of the packets does not allow for any complex routing computation.