### Computer Science Department Technical Report University of California Los Angeles, CA 90024-1596

# ARCHITECTURAL AND COMPILER SUPPORT FOR EFFICIENT FUNCTION CALLS

Miquel Huguet

September 1989 CSD-890051

#### UNIVERSITY OF CALIFORNIA

### Los Angeles

Architectural and Compiler Support for Efficient Function Calls

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy in Computer Science

by

Miquel Huguet

© Copyright by

Miquel Huguet

1989

The dissertation of Miquel Huguet is approved.

Kenneth W. Martin Richard R. Muntz Tomás Lang, Committee Chair

University of California, Los Angeles

1989

In the memory of my father and my Aunt Mercè who left us during this journey, and to my mother and my sister, for all their love, support, and encouragement.

To Laia and Robert Michael who have just started their journey in life.

# Contents

| 1 | Int | roducti  | on                                                 | 1  |

|---|-----|----------|----------------------------------------------------|----|

|   | 1.1 | The P    | roblem and Our Research Contributions              | 1  |

|   | 1.2 | The Bl   | lock-and-Actions Generator                         | 6  |

|   | 1.3 | Progra   | ms Measured                                        | 10 |

|   | 1.4 | Organi   | zation of this Dissertation                        | 13 |

| 2 | Pre | evious a | and Related Work                                   | 15 |

|   | 2.1 | Previo   | us Work                                            | 15 |

|   |     | 2.1.1    | Multiple-Window Architectures                      | 15 |

|   |     | 2.1.2    | Single-Window Architectures                        | 21 |

|   |     | 2.1.3    | Register Allocation and Assignment                 | 22 |

|   |     | 2.1.4    | Performance Studies on Register Allocation         | 35 |

|   |     | 2.1.5    | Performance Evaluation of New Architectures        | 39 |

|   | 2.2 | Related  | l Work                                             | 43 |

|   |     | 2.2.1    | Cache versus Registers                             | 43 |

|   |     | 2.2.2    | Instruction Format (RISC versus CISC)              | 45 |

| 3 | RSI | R Archi  | itectural Support for Single-Window Register Files | 47 |

|   | 3.1 | Static I | Policies A and B                                   | 54 |

|   | 3.2 | Policies | C and D                                            | 55 |

|   | 3.3 | Policies | EFG and H                                          | 60 |

|   | 3.4  | An Example for the Eight RSR Policies                | 66  |

|---|------|------------------------------------------------------|-----|

|   | 3.5  | On the Implementation of Policy G                    | 66  |

|   | 3.6  | Summary                                              | 73  |

| 4 | RS   | R Intra-Procedural Optimizations                     | 75  |

|   | 4.1  | Compiler Support to Reduce the RSR Traffic           | 77  |

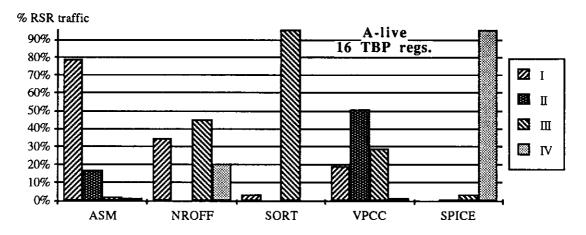

|   |      | 4.1.1 Policy A-live                                  | 77  |

|   |      | 4.1.2 Policy A-live Optimized (A-lvOpt)              | 80  |

|   |      | 4.1.3 Policies B, C, and G with Leaf Functions       | 82  |

|   |      | 4.1.4 Policies C-live and G-live with Leaf Functions | 86  |

|   |      | 4.1.5 Summary                                        | 91  |

|   | 4.2  | A Comparison with Other Register Allocators          | 93  |

|   | 4.3  | A Comparison with SPICE                              | 98  |

|   | 4.4  | A Comparison with Multiple-Window Register Files     | 101 |

|   | 4.5  | Overall Data Memory Traffic Generated                | 106 |

|   | 4.6  | Speed-Up                                             | 111 |

|   | 4.7  | Summary                                              | 114 |

| 5 | Inte | r-Procedural Optimizations                           | 117 |

|   | 5.1  | The Inter-Procedural Optimizer                       | 120 |

|   | 5.2  | Register Allocation for Global Scalar Variables      | 123 |

|   | 5.3  | Return-Address Inter-Procedural Optimization         | 127 |

|   | 5.4  | RSR Inter-Procedural Optimizations                   | 136 |

|   |      | 5.4.1 Global Policy A-live                           | 137 |

|   |      | 5.4.2 Global Policy A-lvOpt                          | 148 |

|   |      | 5.4.3 Global Policy B-lf                             | 156 |

|   |      | 5.4.4 Global Policy G-lf                             | 166 |

|   |      | 5.4.5 Summary                                        | 175 |

|    | 5.5        | Genera   | al-Purpose Register Set Partition                           |          | 177 |

|----|------------|----------|-------------------------------------------------------------|----------|-----|

|    |            | 5.5.1    | Overall Data Memory Traffic Reduction for the Four Programs | 5        | 178 |

|    |            | 5.5.2    | Overall Data Memory Traffic Reduction for SPICE             |          | 181 |

|    |            | 5.5.3    | Speed-Up                                                    |          | 183 |

|    | 5.6        | Summ     | ary                                                         |          | 185 |

| 6  | Con        | ıclusioı | ns and Future Work                                          |          | 189 |

|    | 6.1        | Conclu   | asions                                                      |          | 189 |

|    | 6.2        | Sugges   | stions for Future Work                                      |          | 191 |

| A  | On         | Intra-I  | Procedural Register Allocation                              |          | 195 |

|    | <b>A.1</b> | Selecti  | on Mechanism for Local Scalars                              |          | 196 |

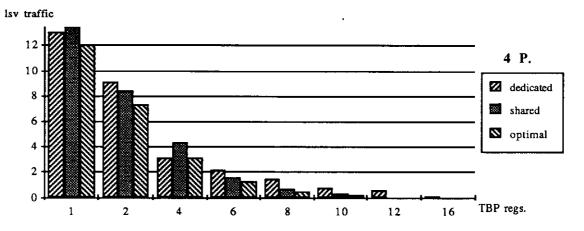

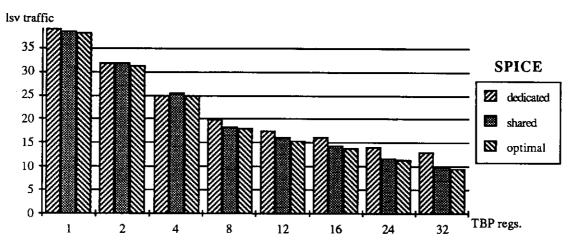

|    | A.2        | Dedica   | ated versus Shared Registers for Local Scalars              | <b>.</b> | 199 |

| Bi | bliog      | raphy    |                                                             |          | 203 |

# List of Figures

| 1.1 | Operations to Be Performed on a Function Call                   | 2  |

|-----|-----------------------------------------------------------------|----|

| 1.2 | Gathering Measurements for the PM on the EM                     | 6  |

| 1.3 | One-to-One Block Mapping                                        | 7  |

| 1.4 | PM to EM Block Translation                                      | 8  |

| 1.5 | Gathering Type II Measurements with BKGEN                       | 10 |

| 2.1 | Multiple-Window Register Files                                  | 16 |

| 2.2 | 64-Shift-Register File with Three-Size Windows                  | 19 |

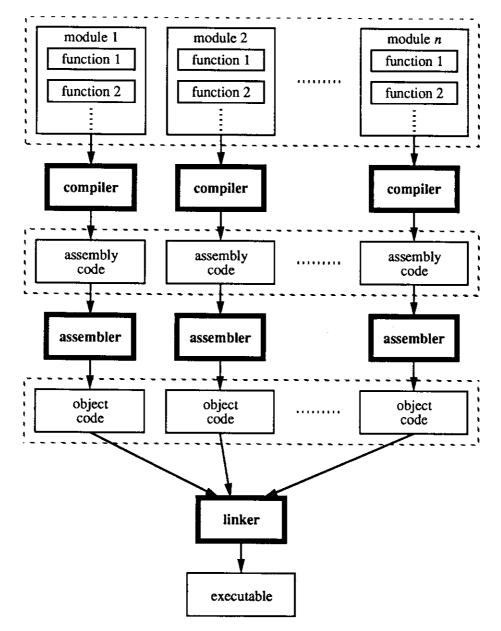

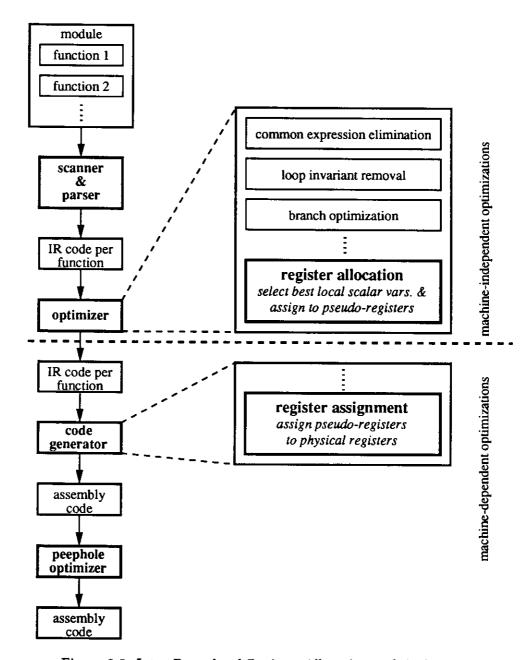

| 2.3 | A Global View of the Compilation Process                        | 24 |

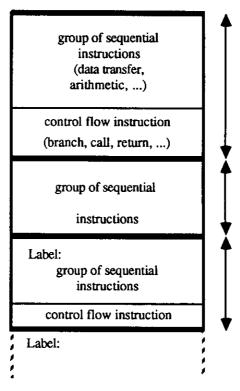

| 2.4 | Basic Blocks                                                    | 25 |

| 2.5 | Intra-Procedural Register Allocation and Assignment             | 27 |

| 2.6 | General-Purpose Register Set Partition                          | 30 |

| 2.7 | Gathering Measurements with the Step-by-Step Instruction Tracer | 41 |

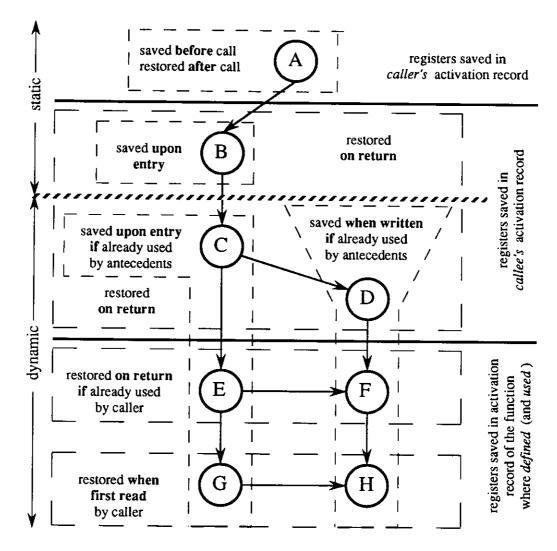

| 3.1 | Relation among the Register Saving/Restoring Policies           | 49 |

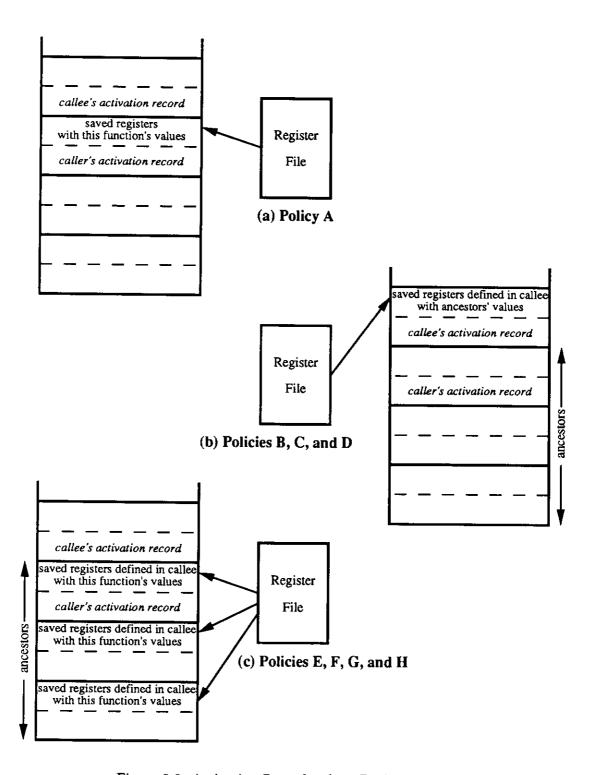

| 3.2 | Activation Records where Registers Are Saved                    | 51 |

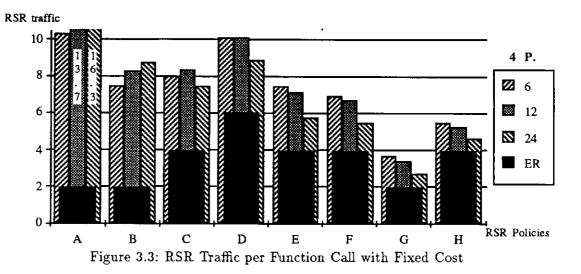

| 3.3 | RSR Traffic per Function Call with Fixed Cost                   | 53 |

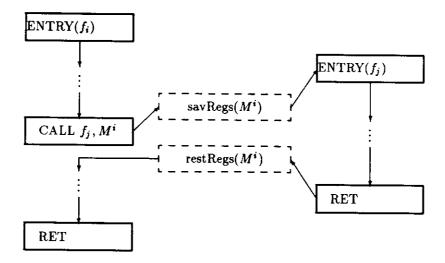

| 3.4 | Policy A                                                        | 54 |

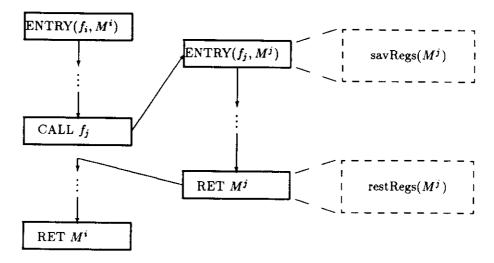

| 3.5 | Policy B                                                        | 55 |

| 3.6 | Policy C                                                        | 56 |

| 3.7 | Policy D                                                        | 59 |

| 3.8 | Policy D versus Policy C                                        | 59 |

| 3.9  | Policy E versus Policy D                                         | 60 |

|------|------------------------------------------------------------------|----|

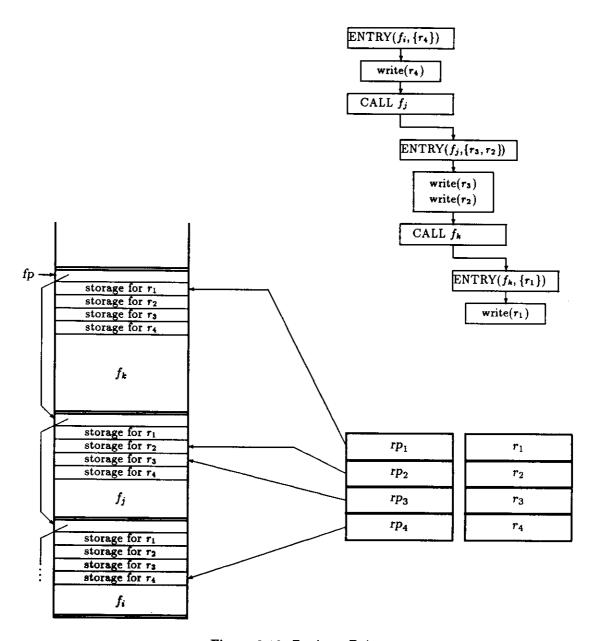

| 3.10 | Register Pointers                                                | 61 |

| 3.11 | Policy E                                                         | 62 |

| 3.12 | Policy F                                                         | 63 |

| 3.13 | Policy G                                                         | 64 |

| 3.14 | Policy H                                                         | 64 |

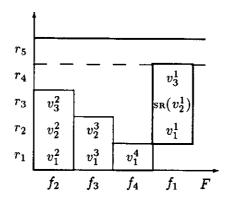

| 3.15 | Example of RSR Traffic Caused by the Different Policies          | 67 |

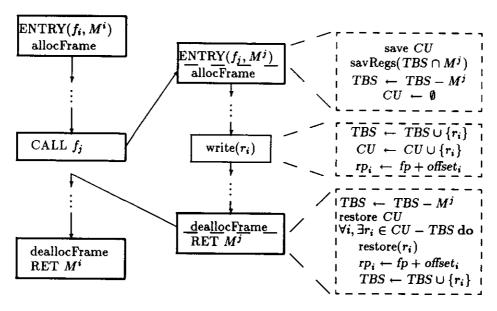

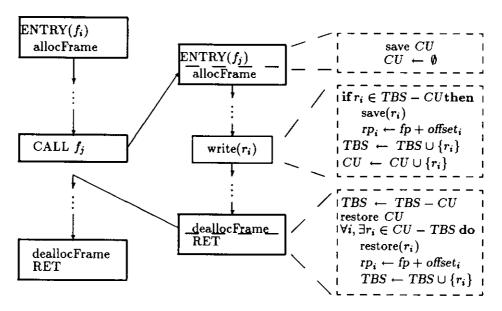

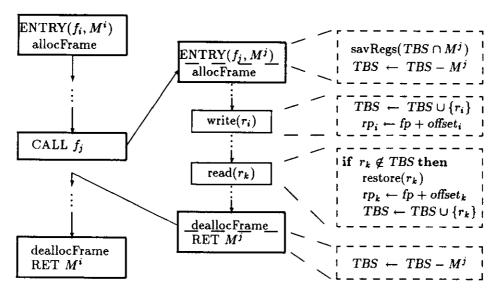

| 3.16 | Implementation of Policy G                                       | 69 |

| 3.17 | RISC-like Pipeline without Restoring                             | 70 |

| 3.18 | RISC-like Pipeline with Restoring                                | 71 |

| 3.19 | Critical Path for a Restoring Operation                          | 72 |

| 3.20 | Critical Path for a Saving Operation                             | 72 |

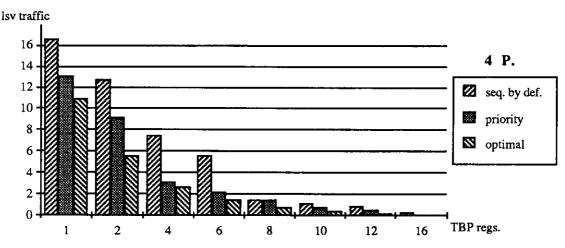

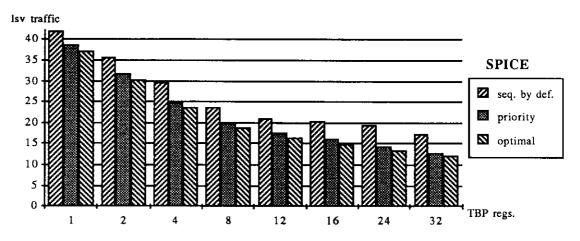

| 4.1  | Policy A-live versus Policy A                                    | 70 |

| 4.2  |                                                                  |    |

|      | Policy A-lvOpt versus Policy A-live                              |    |

| 4.3  | RSR Traffic for Policies A-live and A-lvOpt                      |    |

| 4.4  | Leaf-Function Optimization for the Return Address                |    |

| 4.5  | RSR Traffic for Leaf-Function Optimization (Policies B and G)    | 85 |

| 4.6  | RSR Traffic for Leaf-Function Optimization (Policies B and C)    | 85 |

| 4.7  | Example for Policy G-live                                        | 86 |

| 4.8  | RSR Traffic for Policy G-live                                    | 89 |

| 4.9  | RSR Traffic for Policy G-live with Clear-TBS Instruction Traffic | 90 |

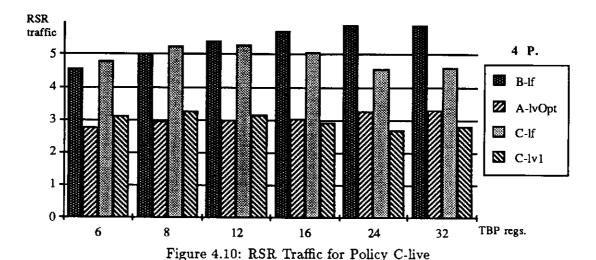

| 4.10 | RSR Traffic for Policy C-live                                    | 91 |

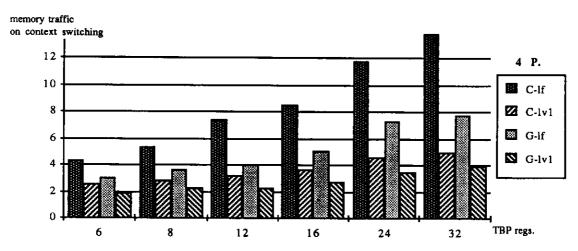

| 4.11 | Average Number of Registers To Be Saved During Context Switching | 92 |

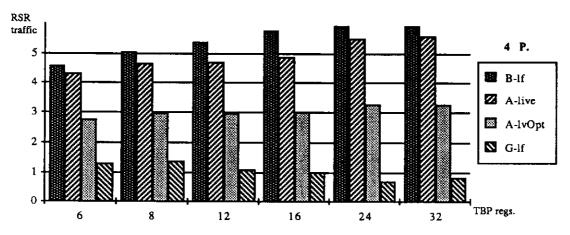

| 4.12 | RSR Traffic for Optimized Policies                               | 92 |

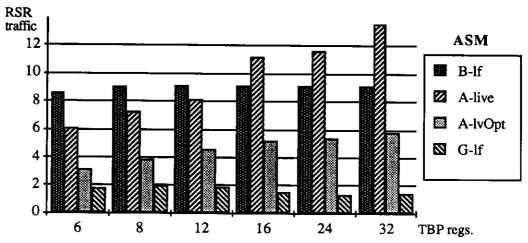

| 4.13 | ASM RSR Traffic for Optimized Policies                           | 93 |

| 4.14 | RSR Traffic for Policy B-lf                                      | 96 |

| 4 15 | RSR Traffic for Policy Galf                                      | 97 |

| 4.16 | RSR Traffic for Policies A-live and A-lvOpt                            |

|------|------------------------------------------------------------------------|

| 4.17 | RSR Traffic for GNU Compiler                                           |

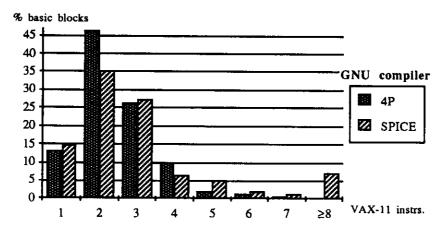

| 4.18 | VAX-11 Instructions per Executed Basic Block                           |

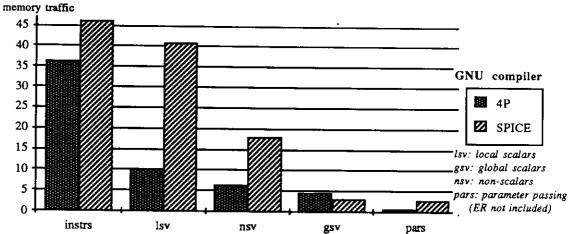

| 4.19 | Data Memory Traffic per Executed Function                              |

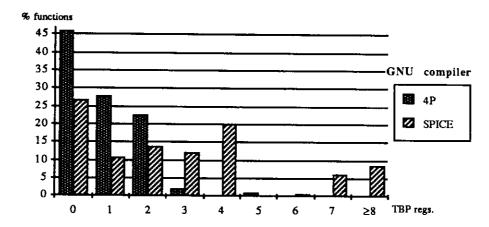

| 4.20 | To-Be-Preserved Registers Required per Executed Function 99            |

| 4.21 | RSR Traffic Generated by the GNU C Compiler for SPICE 100              |

| 4.22 | RSR Traffic for Multiple-Window Register Files                         |

| 4.23 | Average Number of Registers To Be Saved During Context Switching 105   |

| 4.24 | Distribution of Data Memory Traffic                                    |

| 4.25 | Overall Data Memory Traffic with PCC for the Four Programs 107         |

| 4.26 | Overall Data Memory Traffic with GNU for the Four Programs 108         |

| 4.27 | Overall Data Memory Traffic with GNU for SPICE                         |

| 4.28 | Overall Data Memory Traffic Distribution                               |

| 4.29 | Speed-Up for Intra-Procedural Optimizations w.r.t. 0 TBP registers 112 |

| 4.30 | Speed-Up for Intra-Procedural Optimizations w.r.t. Policy B-lf 113     |

| 4.31 | GNU Speed-Up for 12, 16, and 24 TBP registers w.r.t. Policy B-lf 113   |

| 5.1  | Scalar Data Memory Traffic To Be Eliminated                            |

| 5.2  | The Inter-Procedural Optimizer in the Compilation Process              |

| 5.3  | Global Scalar Traffic for the Four Programs                            |

| 5.4  | Global Scalar Traffic for SPICE                                        |

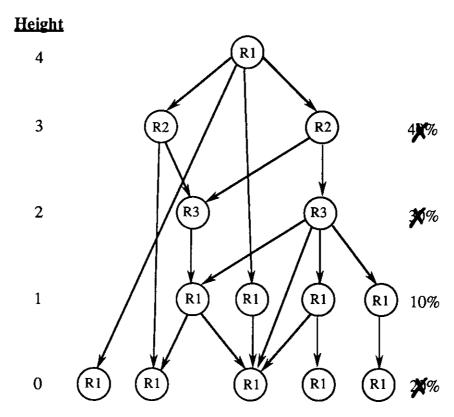

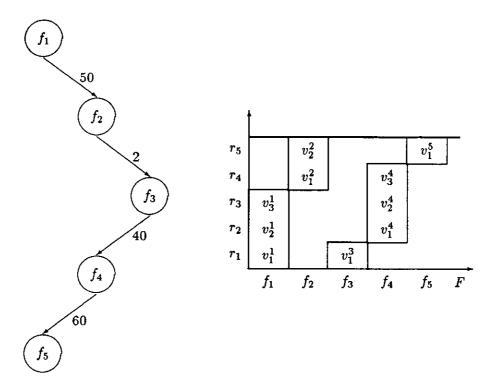

| 5.5  | Function Execution Frequency in a Call Graph                           |

| 5.6  | Register Assignment with Three-Link Registers                          |

| 5.7  | A Better Register Assignment with Three-Link Registers                 |

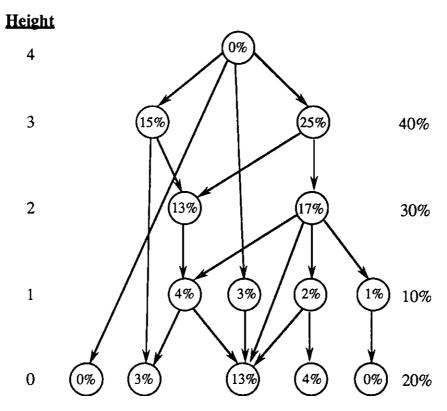

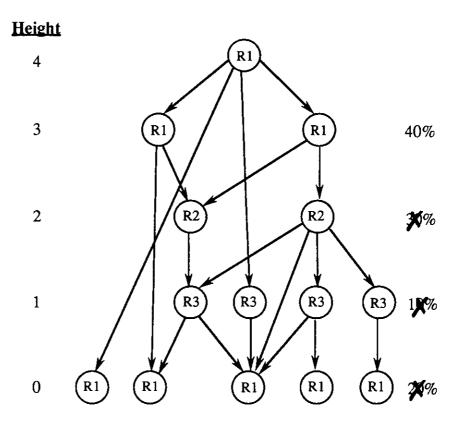

| 5.8  | Distribution of Functions by Height                                    |

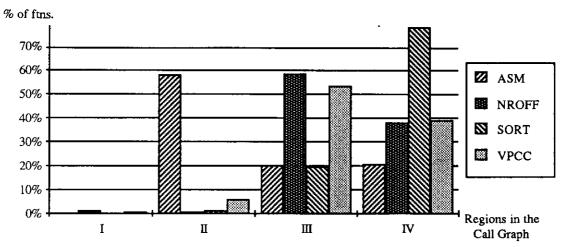

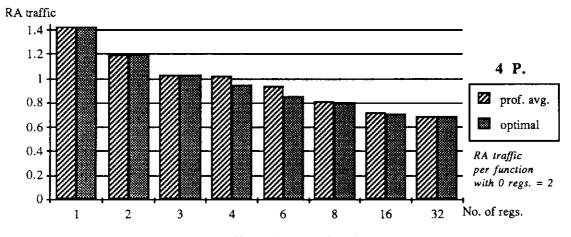

| 5.9  | RA Traffic Reduction for the Four Programs                             |

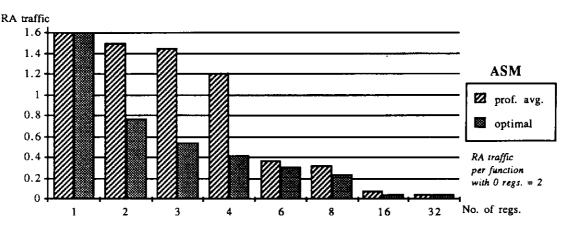

| 5.10 | RA Traffic Reduction for ASM                                           |

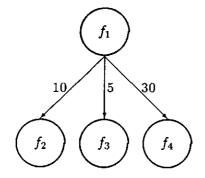

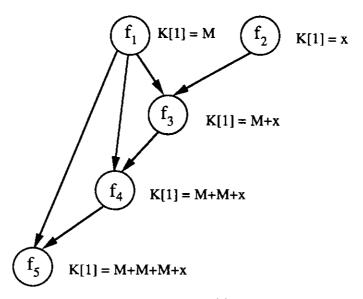

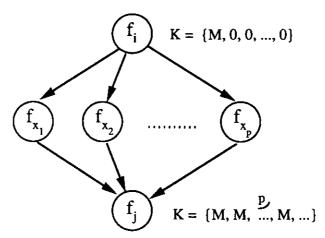

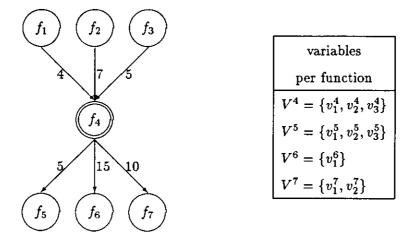

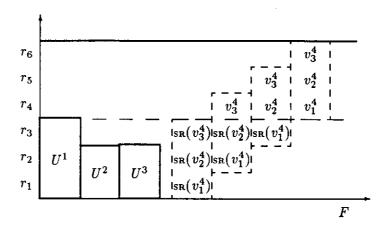

| 5.11 | An Example of Register Assignment for Policy Ag-live                   |

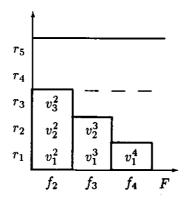

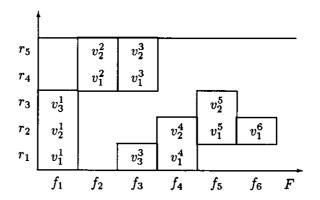

| 5.12 | Registers Assigned to Functions $f_2$ , $f_3$ , and $f_4$          |

|------|--------------------------------------------------------------------|

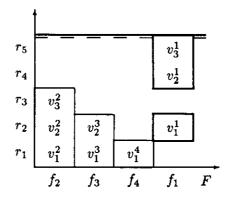

| 5.13 | Variable-to-Register Assignment for Function $f_1$                 |

| 5.14 | Distribution of the RSR Traffic Caused by Policy A-live            |

| 5.15 | Variable-to-Register Assignment for Function $f_1$ when $K=11$ 140 |

| 5.16 | Register Assignment for Policy Ag-live                             |

| 5.17 | Wrong Computation for $K[i]$ when Values Are Added                 |

| 5.18 | K Values with Two Passes                                           |

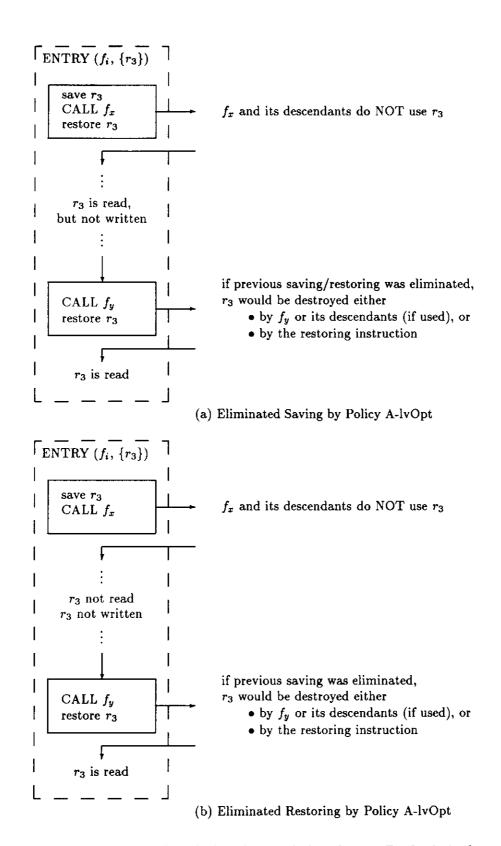

| 5.19 | Cases for which Policy Ag-lvOpt Cannot Be Optimized                |

| 5.20 | Policy Ag-lvOpt versus Policy A-lvOpt                              |

| 5.21 | Register Assignment for Policy Ag-lvOpt                            |

| 5.22 | Distribution of the RSR Traffic Caused by Policy A-lvOpt           |

| 5.23 | RSR Traffic Generated by Policies Ag-live and Ag-lvOpt             |

| 5.24 | Distribution of Functions by Depth                                 |

| 5.25 | Distribution of the RSR Traffic Caused by Policy B-lf              |

| 5.26 | An Example of Register Assignment for Policy B <sup>8</sup> -lf    |

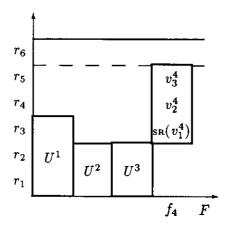

| 5.27 | Alternative Register Assignments for Function $f_4$                |

| 5.28 | Optimal Variable-to-Register Assignment for Function $f_4$         |

| 5.29 | Register Assignment for Policy Bg-lf                               |

| 5.30 | Alternative Register Assignments for Algorithm 3                   |

| 5.31 | RSR Traffic for Policy B <sup>g</sup> -lf                          |

| 5.32 | Disjoint Register Assignment for Policy Gg-lf                      |

| 5.33 | An Example of Register Assignment for Policy G <sup>g</sup> -lf    |

| 5.34 | Variable-to-Register Assignment                                    |

| 5.35 | Register Assignment for Policy Gg-lf                               |

| 5.36 | RSR Traffic for Policy Gg-lf                                       |

| 5.37 | Inter-Procedural Optimized RSR Traffic for the Four Programs 172   |

| 5.38 | Inter-Procedural Optimized RSR Traffic for SPICE                   |

| 5.39 | Policy                                                                |

|------|-----------------------------------------------------------------------|

| 5.40 | Data Memory Traffic for the Four Programs with Policy $G^{g}$ -lf 179 |

| 5.41 | Remaining Data Memory Traffic for the Four Programs                   |

| 5.42 | Data Memory Traffic for SPICE with the Best Static Global Policy 182  |

| 5.43 | Data Memory Traffic for SPICE with Policy $G^{g}$ -lf                 |

| 5.44 | Remaining Data Memory Traffic for SPICE                               |

| 5.45 | Speed-Up for Inter-Procedural Optimizations w.r.t. Policy B-lf 184    |

| 5.46 | Speed-Up for Inter-Procedural Optimizations w.r.t. Policy G-lf 185    |

| A.1  | Local Scalar Traffic for the Four Programs                            |

| A.2  | Local Scalar Traffic for SPICE                                        |

| A.3  | Dedicated versus Shared Registers for the Four Programs 201           |

| A.4  | Dedicated versus Shared Registers for SPICE                           |

# List of Tables

| 1.1  | Large Programs Measured by Some Other Studies                      | 12  |

|------|--------------------------------------------------------------------|-----|

| 2.1  | Multiple-Window Processors                                         | 17  |

| 2.2  | Single-Window Processors                                           | 22  |

| 2.3  | Features for Several Register Allocators                           | 36  |

| 3.1  | Register Saving/Restoring Policies                                 | 48  |

| 3.2  | RSR Traffic Relative to Policy B                                   | 52  |

| 3.3  | Hardware Implementation for Set Operations                         | 56  |

| 4.1  | RSR Traffic for Policy A Optimizations Relative to Policy B        | 79  |

| 4.2  | Percentage of Consecutive Calls                                    | 81  |

| 4.3  | Percentage of Leaf Functions                                       | 83  |

| 4.4  | RSR Traffic for Leaf-Function Optimization Relative to Policy B    | 84  |

| 4.5  | RSR Traffic for Policies C-live and G-live Relative to Policy G-lf | 87  |

| 4.6  | Percentage of Calls which Issue a Clear-TBS Instruction            | 88  |

| 4.7  | RSR Traffic Generated by ACK and GNU Relative to PCC Policy B-lf   | 95  |

| 4.8  | RSR Traffic for Multiple-Window Register Files                     | .02 |

| 4.9  | Percentage of Functions which Must Expand the Window Size          | .03 |

| 4.10 | Percentage of Overflows in Multiple-Window Register Files          | 04  |

| 4.11 | Average Number of Registers To Be Saved During Context Switching 1 | .05 |

| 5.1  | Input Data for Profiling the Measured Programs                     | 24  |

| 5.2  | Global Scalar Traffic Reduction                              |

|------|--------------------------------------------------------------|

| 5.3  | Percentage of Functions in a Cycle                           |

| 5.4  | RA Traffic Reduction with Inter-Procedural Optimization      |

| 5.5  | RA Traffic Reduction with Multiple PCs                       |

| 5.6  | RSR Traffic Reduction for Policy Ag-live                     |

| 5.7  | RSR Traffic Reduction for Policy Ag-lvOpt                    |

| 5.8  | RSR Traffic Reduction for Policy Bg-lf                       |

| 5.9  | RSR Traffic Reduction for Policy $G^g$ -lf                   |

| 5.10 | RSR Traffic Reduction for the Global Policies                |

| A 1  | Local Scalar Traffic Paduction                               |

| A.1  | Local Scalar Traffic Reduction                               |

| A.2  | Local Scalar Traffic with Dedicated and Shared Registers 200 |

#### ACKNOWLEDGMENTS

Many people have helped me during my 7-year journey at UCLA. I would like to thank them, because without the positive learning environment which they helped create, this dissertation would not have been finished.

Tomás has been an excellent mentor. He has been a role model for both my teaching and research, has always pushed me to find better and more efficient algorithms, and has offered innumerable suggestions to improve the readability and the content of my drafts. Tomás and Diana were marvelous hosts upon my arrival to Los Angeles, making my transition smooth and happy.

Dick, Miloš, and Dave Martin have also been terrific teachers and have encouraged me to improve my teaching skills. Dick has also offered advice on linear optimization. Yuval has provided suggestions on how to perform architecture measurements and positive criticism on the implementation of one of the architectural policies proposed in this dissertation. Mateo and Jordi Cortadella have also commented on previous drafts.

Maria Eugenia and Hector, Marisa and Jaime, Ravi, Brett, Leon, Martine and Pak, Marc, Frank, Doris, Art, Verra, Jeong-A, and Paul have helped to create a warm and stimulating environment in the Computer Science Department where research and personal growth have been possible.

Marisol and Robert, Josefina, Olga, Pilar, Maribel and Jordi, Luisa and Edward, Magda, Andolin, Jon, Neil, Chris, Darren, and Tim have been my adopted family in Los Angeles, have made life in the city more bearable and lively, and provided me with an emotional support during the period of time that we have enjoyed together. Also, Neil has proofread this manuscript.

FULBRIGHT/MEC, CIRIT, and GTE provided financial support during my studies at UCLA.

To all, thank you very much!

#### VITA

| March 27, 1956 | Born in Alforja, El Baix Camp de Catalunya, Spain                                                                 |

|----------------|-------------------------------------------------------------------------------------------------------------------|

| 1979           | Licenciado en Informática<br>Universitat Politècnica de Catalunya, Barcelona                                      |

| 1979           | National Award for Best Student in Computer Science                                                               |

| 1980-1982      | Ministry of Education, Young Researchers Fellowship                                                               |

| 1980–1982      | Lecturer<br>Universitat Politècnica de Catalunya, Barcelona                                                       |

| 1981           | Licenciado con Grado en Informática<br>Universitat Politècnica de Catalunya, Barcelona                            |

| 1982-1984      | FULBRIGHT/MEC Fellowship                                                                                          |

| 1984–1989      | Teaching Assistant, Associate, and Fellow<br>Computer Science Department<br>University of California, Los Angeles |

| 1984–1986      | CIRIT (Generalitat de Catalunya) Fellowship                                                                       |

| 1985           | Master of Science in Computer Science<br>University of California, Los Angeles                                    |

| 1987–1988      | GTE Fellowship                                                                                                    |

| 1989           | Distinguished Teaching Award<br>Computer Science Department<br>University of California, Los Angeles              |

#### PUBLICATIONS AND PRESENTATIONS

- 1. M. Huguet and T. Lang, "Reduced Register Saving/Restoring for Small Register Files," UCLA Technical Report CSD-880066, August 1988.

- 2. M. Huguet, "Architectural and Compiler Support for Efficient Function Calls: A Proposal," UCLA Technical Report CSD-880030, June 1988.

- 3. M. Huguet, T. Lang, and Y. Tamir, "A Block-and-Actions Generator as an Al-

- ternative to a Simulator for Collecting Architecture Measurements," *Proc.* of the SIGPLAN'87 Symp. on Interpreters and Interpretive Techniques, June 1987, pp. 14–25.

- T. Lang and M. Huguet, "Reduced Register Saving/Restoring in Single-Window Register Files," Computer Architecture News, Vol. 14, No. 3, June 1986, pp. 17-26.

- 5. M. Huguet and T. Lang, "A Reduced Register File for RISC Architectures," Computer Architecture News, Vol. 13, No. 4, September 1985, pp. 22-31.

- M. Huguet and T. Lang, "A C-Oriented Register Set Design," Proc. of the 29th Symposium on Mini and Microcomputers and Their Applications, June 1985, pp. 182-189.

- 7. M. Huguet, "A C-Oriented Register Set Design," Master's Thesis, University of California, Los Angeles, June 1985.

- 8. M. Huguet, "The Protection of the Processor Status Word of the PDP-11/60," Computer Architecture News, Vol. 10, No. 4, June 1982, pp. 27-30.

- 9. M. Huguet, "Monitorització del Sistema Operatiu RSX-11M," Minor Thesis, Facultat d'Informàtica, Universitat Politècnica de Catalunya, December 1981.

#### ABSTRACT OF THE DISSERTATION

Architectural and Compiler Support for Efficient Function Calls

by

Miquel Huguet

Doctor of Philosophy in Computer Science

University of California, Los Angeles, 1989

Professor Tomás Lang, Chair

With the current trend towards VLSI load/store architectures, registers have become one of the critical resources for increasing processor performance. One of the important factors which influences the design and use of a register file is the overhead produced by the register saving and restoring (RSR). This dissertation investigates the support that the architecture can provide to implement efficient function calls for single-window architectures combined with the support that can be provided by the compiler. Several architectural policies which reduce the RSR overhead for single-window architectures are presented. These policies make use of dynamic information to determine which registers have been used during program execution. They are evaluated and compared to the conventional static policies for single-window architectures (to save/restore registers at the caller or at the callee) and to the already-existing schemes for multiple-window architectures (fixed-size windows, variable-size windows, and multi-size windows). We show that one of our dynamic policies reduces significantly the RSR traffic with respect to the conventional static policies and that most of its activities are performed in parallel with the main CPU activities.

Six new compiler optimizations to reduce the RSR traffic are also presented. Two of them are *intra-procedural* and are based on live-variable analysis. The other four are *inter-procedural* and their goal is to find a *register assignment* so that unnecessary RSR can be eliminated. These optimizations are also evaluated and compared to the already-existing intra-procedural optimizations (leaf functions and live-variable analysis) and to

other inter-procedural register allocation schemes. The inter-procedural optimizer not only reduces the RSR traffic, but also the global scalar traffic and the return-address traffic.

We show that a combination of both architectural and compiler support, i.e., our dynamic policy with either intra-procedural or inter-procedural optimizations, is the best approach; it generates less data memory traffic than when only either architectural or compiler support is provided. Also, it simplifies the compilation process.

Both the architectural and the compiler policies have been evaluated with a new tool, the *Block-and-Actions Generator*, which substantially reduces the overhead introduced by a conventional simulator, the tool traditionally used to obtain these types of measurements. The Block-and-Actions Generator's main advantage is that, since the execution time is substantially reduced, *large typical* programs can be measured—the NROFF word processor, the SORT program, the VAX-11 assembler, the Portable C Compiler, and SPICE, a VLSI circuit simulator.

## Chapter 1

### Introduction

In this introductory chapter we offer first a description of the problem that this dissertation addresses and a summary of our contributions towards its solution (Section 1.1). Second, we present our tool to perform the measurements discussed in this work (Section 1.2) and the programs measured (Section 1.3). Finally, we give the general outline of this dissertation (Section 1.4).

#### 1.1 The Problem and Our Research Contributions

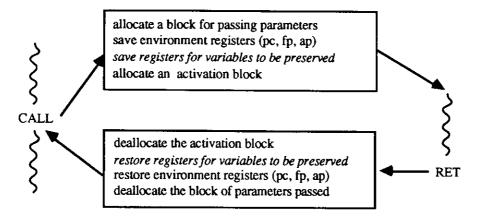

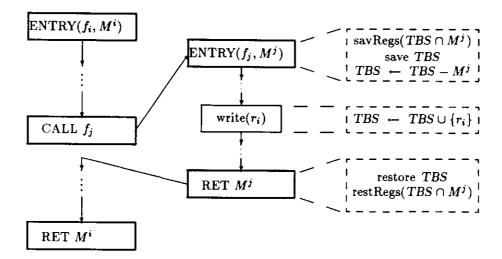

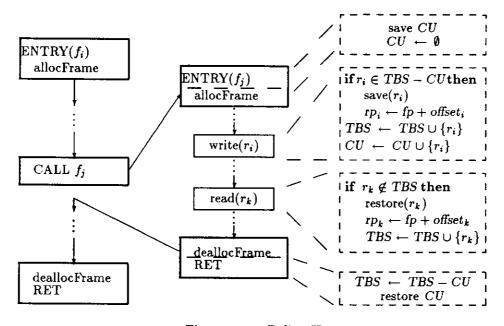

With the current trend towards VLSI load/store architectures, registers have become one of the critical resources to increase processor performance [Patt82b, Radi82, Henn84, Patt85a]. Recent advances in compiler technology, especially in register allocation optimization [Chai82, Ankl82, Chow83, Wall86, Stee87, Chow88], have resulted in better use of the register set because the compiler can allocate more scalar variables to registers. The use of registers reduces the data memory traffic, because whenever operands are already available in processor registers, no memory address has to be calculated and no memory access has to be generated. The use of registers also reduces the instruction memory traffic because shorter addresses are used, and for load/store architectures no load (store) instruction has to be generated to fetch (transfer) the operand from (to) memory. However, registers have to be saved every time a procedure or function is called, and restored when the function returns (see Figure 1.1). It has been observed that one of the important factors which influences the design and use of the register set is the overhead produced by the register saving and restoring (RSR).

For instance, Lunde [Lund77] affirms that the BLISS compiler spends 25% of its execution time compiling the program "Treesort" in call administration. Patterson and Séquin [Patt82b] have weighted the relative frequency of C-language [Kern78] statements to conclude that 12% of the statements are calls and that they correspond to 33% of the machine instructions and to 45% of the memory references. (These numbers have been computed from the average number of instructions and references per statement

Figure 1.1: Operations to Be Performed on a Function Call

generated by the C compilers for VAX-11, PDP-11, and MC68000.) The RSR overhead becomes more significant for languages such as C, which encourage the use of functions.

To reduce the RSR overhead some current processors rely on hardware support, such as multiple-window register files [Patt82b, Kate83, Unga84, Atki87, Ditz87c], intraprocedural optimizations [Radi82, Chow84], and/or inter-procedural optimizations [Wall86, Stee87, Chow88, Rich89].

Multiple-window architectures have divided the register file into a set of banks or windows. When a function is called, a new window of registers is made active [Site79a, Dann79, Lamp82], so that registers have to be saved only when no more free windows are available in the register file. In contrast, processors with the conventional general-purpose register file directly addressable by each function are classified as single-window architectures.

Although multiple-window architectures produce a large reduction in the RSR traffic [Patt82a, Patt82b, Hugu85a, Flyn87], they have three main drawbacks: they use a large chip area in a VLSI implementation or a large number of chips in a MSI/LSI implementation; they increase the amount of processor context to be saved on context switching; and they increase the processor cycle-time due to the long data busses [Henn84, Sher84]. These drawbacks are discussed in Subsection 2.1.1.

Due to these drawbacks, several processors prefer to have the conventional single-window register file and rely on compiler optimizations to reduce the RSR overhead, such as live-variable analysis [Hech77, Aho86] and leaf-function optimization (as used in the compilers for MIPS [Chow86] and for HP-Spectrum [Cout86b]). These optimizations are discussed in Subsection 2.1.3.4. However, the compiler complexity is increased. To reduce the cost of developing an optimizing compiler for every language and every machine [John81], current research on optimizing compilers pursues the independence of the optimizations from both the source language and the target machine

<sup>&</sup>lt;sup>1</sup>VAX-11 and PDP-11 are trademarks of Digital Equipment Corporation.

[Perk79, Alle80, Ausl82, Tane83, Powe84]. This is also true for the algorithms which perform register allocation [John75, Site79b, Leve83, Chow83].

This dissertation investigates both the support that the architecture can provide to implement efficient function calls in single-window architectures and the support that can be provided by the compiler. By architectural support we mean the hardware included in the processor to implement a specific RSR operation which would be executed much more slowly if it was implemented by the standard set of machine instructions provided. The algorithms which describe the operations to be performed in hardware are called architectural policies. Similarly, compiler support refers to the (software) algorithms provided by the compiler to reduce the number of RSR operations to be performed during execution.

#### The Measurements

Both the architectural and the compiler policies have been evaluated with a new tool: the Block-and-Actions Generator (BKGEN). BKGEN drastically reduces the overhead introduced by a conventional simulator—the tool traditionally used to obtain these types of measurements. Section 1.2 presents BKGEN and Subsection 2.1.5 comments on the overhead introduced by conventional simulators. The main advantage of BKGEN is that, since the execution time is substantially reduced, large typical programs can be measured. The typical UNIX<sup>2</sup> programs measured are: the NROFF word processor, the SORT program, the VAX-11 assembler (ASM), the Portable C Compiler for VAX-11 (VPCC), and SPICE, a VLSI circuit simulator. More information on these programs is given in Section 1.3. Since SPICE has different characteristics than the other four programs (as we mention in Section 1.3 and show in Section 4.3), the measurements presented in this dissertation are usually given separately for SPICE and for the average of the other four programs.

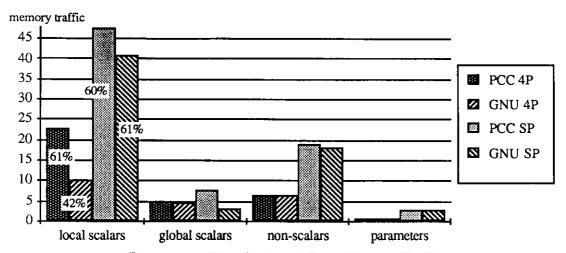

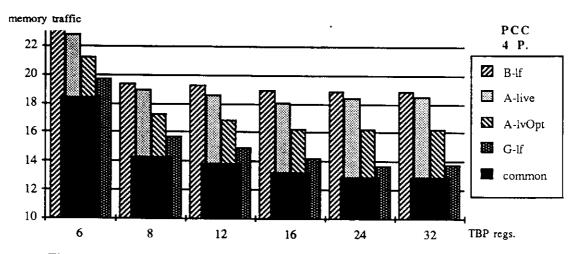

Three compilers have been used in this dissertation to evaluate the data memory traffic generated and the traffic reduction obtained by our new architectural and compiler policies.<sup>3</sup> These compilers are: the Portable C Compiler, PCC [John79], the Amsterdam Compiler Kit, ACK [Tane83], and the GNU C Compiler [Stal88]. These compilers have been modified to generate code for six different register configurations. These configurations correspond to when the register allocator has 6, 8, 12, 16, 24, and 32 registers available for variables to be preserved across function calls (e.g., local scalar variables). The overall data memory traffic generated by these compilers for the above-mentioned programs is divided into the following six categories: local scalar traffic, RSR traffic, global scalar traffic, return-address traffic, parameter-passing traffic, and non-scalar traffic. The traffic caused by expression evaluation is ignored because expressions are evaluated with a small number of registers (see Subsection 2.1.4).

<sup>&</sup>lt;sup>2</sup>UNIX is a registered trademark of AT&T.

<sup>&</sup>lt;sup>3</sup>Each policy has not been evaluated with every compiler, although we expect that similar results would be obtained for any compiler (see Sections 4.2 and 4.5).

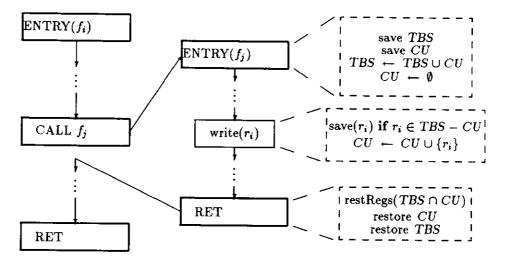

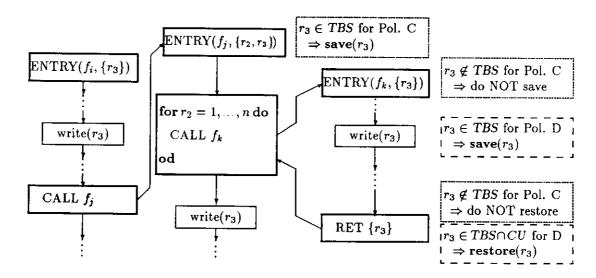

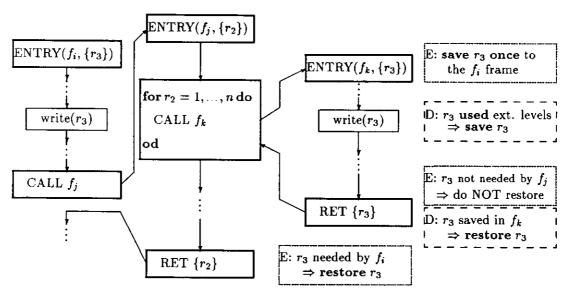

#### RSR Architectural Support

This dissertation presents six new architectural policies to reduce the RSR overhead for single-window architectures. These policies make use of *dynamic* information to know which registers have been used during program execution. They are evaluated and compared to the conventional *static* policies for single-window architectures (to save/restore registers at the caller—named **Policy A**—or at the callee—named **Policy B**) and to the already-existing schemes for multiple-window architectures (fixed-size windows [Kate83], variable-size windows [Ditz82], and multi-size windows [Hugu85a]).

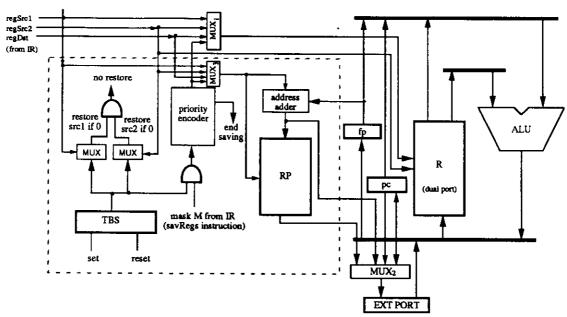

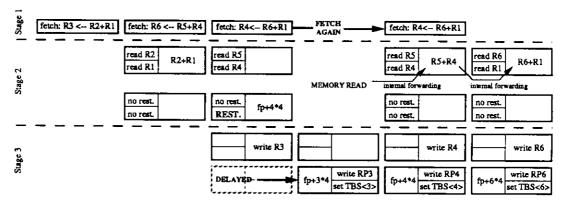

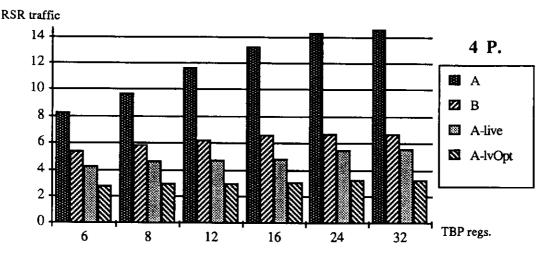

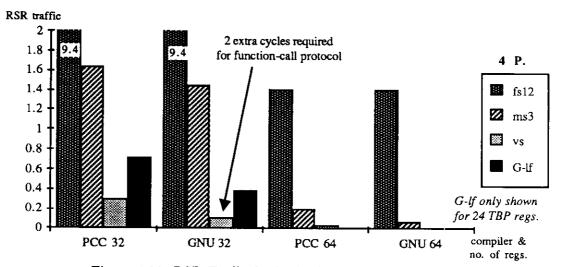

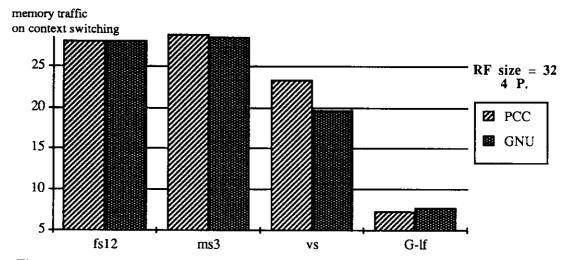

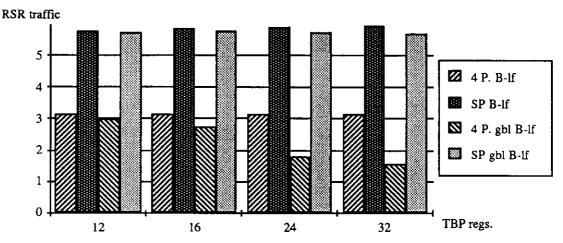

We show that one of the dynamic policies, Policy G, is our best candidate for implementation since it is the one that generates the least RSR traffic. Policy G has between 12% (when 24 registers are available to the allocator) and 31% (for 6) of the RSR traffic generated by Policy B and between 5% (for 24) and 20% (for 6) of Policy A. In addition to reducing the RSR traffic, Policy G also reduces the number of registers to be saved/restored during context switching. We also show that when the register set size is increased, the static Policies A and B generate even more RSR traffic, while this is not the case for the dynamic Policy G. The implementation of Policy G is sketched to show that most of its activities are performed in parallel with the main CPU activities.

#### **RSR Intra-Procedural Optimizations**

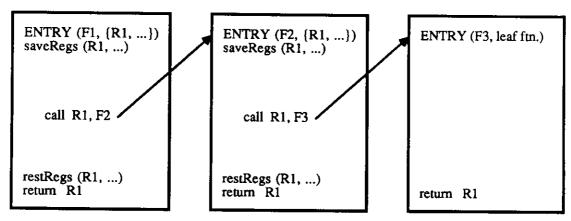

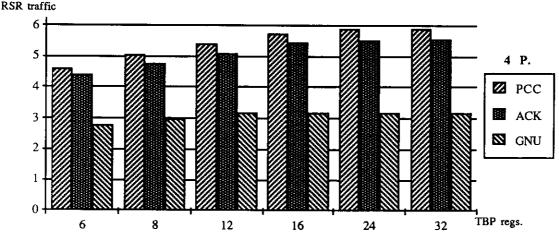

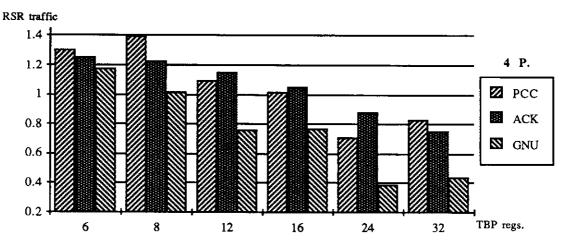

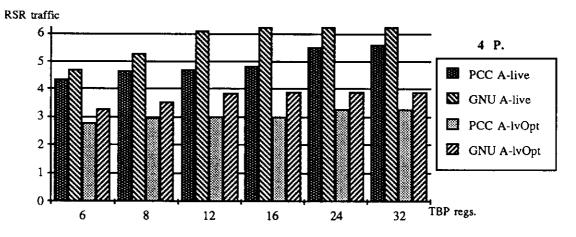

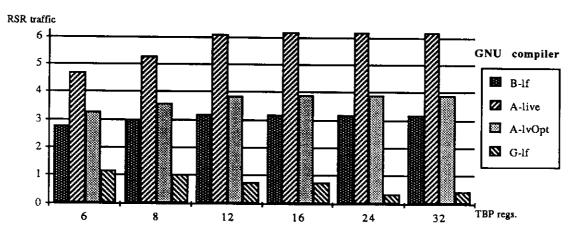

Two new intra-procedural (i.e., performed per function) compiler optimizations are also presented to reduce the RSR traffic. These are based on live-variable analysis: one is for Policy A and the second for Policy G. These optimizations are also evaluated and compared to the already-existing compiler optimizations: live-variable analysis and leaf functions. When intra-procedural optimizations to reduce the RSR traffic are performed, we conclude the following:

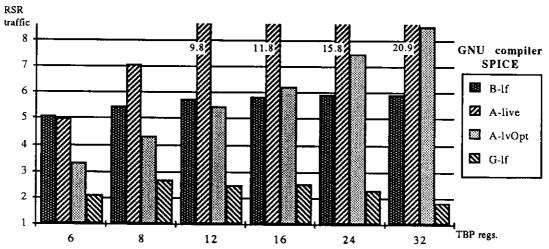

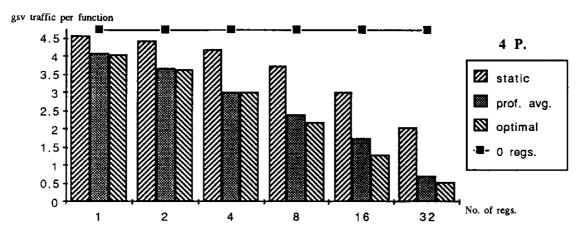

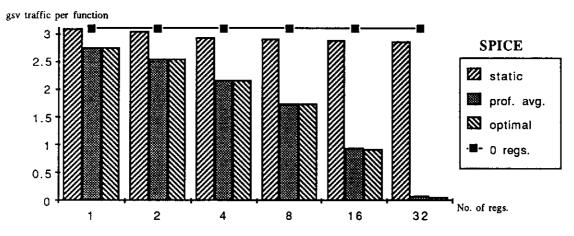

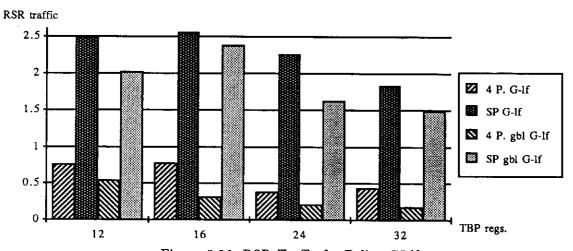

- 1. Policy G with leaf-function optimization (Policy G-lf) is the policy which generates the least traffic for any program and for any of the three compilers used in this dissertation. For instance, with the GNU C Compiler, Policy G-lf has between 13% and 42% of the RSR traffic generated by the best intra-procedural static policy (Policy B-lf) for the average of the four programs and between 31% and 48% for SPICE.

- 2. When only compiler support is provided, our measurements have indicated that there is no best approach for performing the register saving and restoring, either at the caller or at the callee. Depending on the program characteristics, one approach can perform better than the other. Thus, the compiler should let the programmer decide which of the two approaches is the most suitable for a specific application.

- 3. Our measurements have not shown the necessity for having more than 12 registers available to the allocator for non-numeric applications because the reduction in local scalar traffic obtained with a larger number of registers is balanced with the

- increase in RSR traffic. This is not the case for numeric applications, like SPICE, because of its heavier register use.

- 4. When 12 registers are available to the allocator, the overall data memory traffic reduction, when both architectural and compiler support are provided, is 15% for the average of the four programs and 8% for SPICE with respect to when only compiler support is provided.

#### **Inter-Procedural Optimizations**

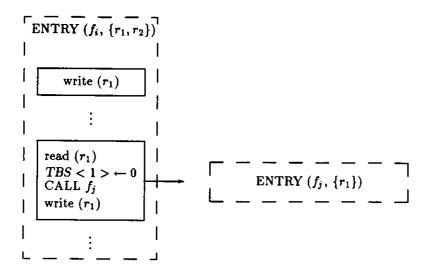

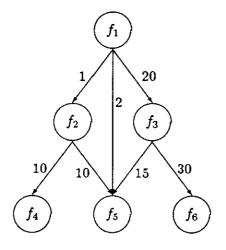

To reduce the RSR traffic further, four new *inter-procedural* (i.e., applied to the whole program) compiler optimizations are also presented. One inter-procedural optimization is based on the dynamic Policy G, the other three on static intra-procedural policies. Their goal is to find a *register assignment* such that unnecessary RSR can be eliminated. Register assignment decides the registers to be used by the variables that have been selected for allocation in a previous phase by the intra-procedural register allocator.

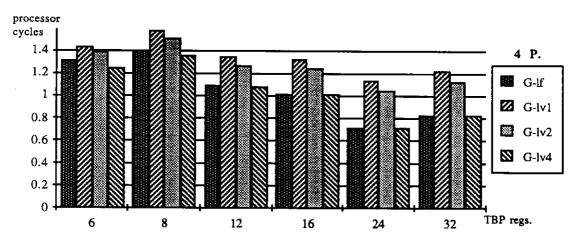

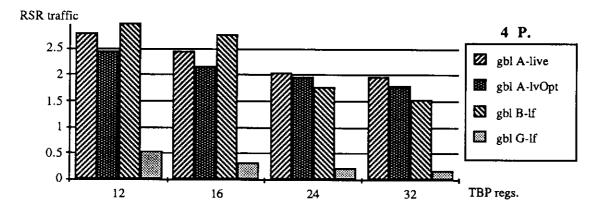

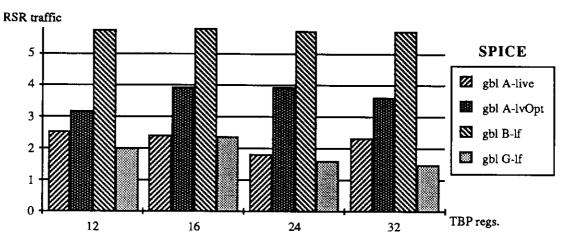

Our inter-procedural optimizer not only reduces the RSR traffic, but also the global scalar traffic and the traffic caused by the return address. The inter-procedural optimizer uses a dynamic execution profile of the programs to obtain a better overall data memory traffic reduction. When inter-procedural optimizations are performed, we conclude the following:

- 1. The Global Policy G with leaf-function optimization (Policy Gg-lf) is the policy which generates less RSR traffic than any of the three proposed static interprocedural policies. For instance, with the GNU C Compiler, the best interprocedural static policy has between 445% (when 12 registers are available to the allocator) and 816% (for 32) of the RSR traffic generated by Policy Gg-lf for the average of the four programs and between 103% and 155% for SPICE.

- 2. When only compiler support is provided, our measurements have indicated that there is no best approach for performing the register saving and restoring among the three static inter-procedural policies. Thus, the inter-procedural optimizer should have all of the policies available to select the most suitable for a specific application. Still, this increases the complexity of the inter-procedural optimizer. On the other hand, Policy Gg-lf not only generates the least RSR traffic, but also is the easiest inter-procedural policy to implement.

- 3. The RSR traffic becomes smaller for larger register sets for all four inter-procedural RSR policies. Thus, the inter-procedural optimizer can efficiently use a larger register set. This is not the case when only intra-procedural optimizations are performed.

- 4. For a 32-general-purpose-register file and for the average of the four programs, the overall data memory traffic reduction when both architectural and compiler

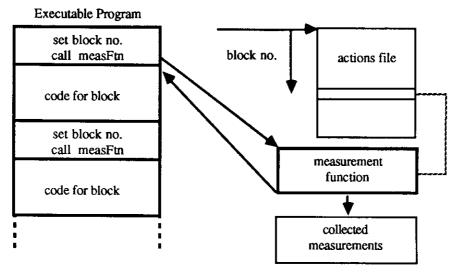

Figure 1.2: Gathering Measurements for the PM on the EM

support are provided, versus when only inter-procedural compiler support is available, is 14%. The overall data memory traffic reduction with respect to the intra-procedural optimizer with Policy G-If is 21%. For SPICE, the overall data memory traffic generated when both architectural and compiler support is provided is the same as the one generated when only compiler support is provided. The reason for this will be discussed in Section 5.5.

Therefore, since Policy  $G^g$ -If usually generates the least data memory than any static inter-procedural policy (with the exception of SPICE), both architectural and compiler support (i.e., Policy  $G^g$ -If) is the best approach to reduce the overall data memory traffic and to simplify the compilation process.

#### 1.2 The Block-and-Actions Generator

Conventional simulators used for collecting dynamic measurements are limited by their execution speed because several hundred instructions are required to decode, interpret, and measure each simulated instruction (see Subsection 2.1.5). To be able to measure large typical programs we have designed a new tool for collecting architectural measurements: the Block-and-Actions Generator (BKGEN).

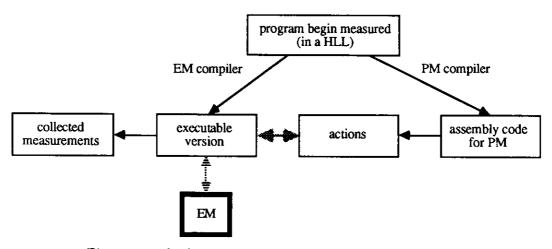

Given a program to be measured (in a high-level language), the goal of BKGEN is to run directly an executable version of this program on an existing machine (EM) while collecting measurements for the proposed machine (PM). This executable version is obtained directly either with the EM compiler or with a combination of the PM compiler and an assembly-to-assembly translator. The choice between these alternatives depends on the EM and PM compiler technology and the type of measurements to be obtained (as we will discuss below). BKGEN also collects the PM events to be measured (called actions). Each EM basic block of instructions is associated with a PM block of actions

Figure 1.3: One-to-One Block Mapping

so that when the program is executed, it collects the measurements associated with the PM (see Figure 1.2).

To present how BKGEN is implemented we explain first how to associate EM blocks to PM blocks and actions; afterwards, we discuss the size of a block and the interception code that has to be added to each EM block to perform the measurements.

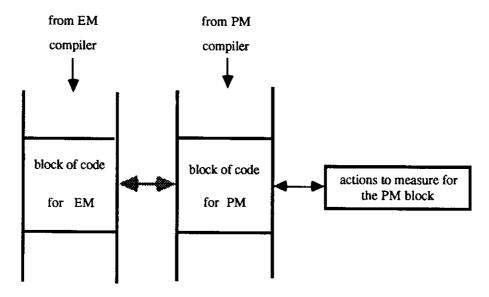

If a number is associated with each block, then the execution flow of a program can be described by the sequence of block numbers. This flow depends mainly on the original program structure, the transformations performed by the compiler, and the input data, but usually not on the processor architecture (some exceptions are discussed in [Hugu87]). Thus, the flow for both the EM and the PM is generally the same. In this case, each block of code for the EM is mapped to a block of code for the PM. This mapping can be performed as follows:

- 1. If the compiler technology used for the PM is the same as (or similar to) the one used for the EM, then it is probable that both compilers generate the same number of blocks and equivalent control flow instructions. If both programs were executed and the trace of executed blocks was identical, we would say that we have a valid mapping (see Figure 1.3). In this case, it is possible to execute machine language instructions of the EM directly and measure the architecture characteristics of the PM.

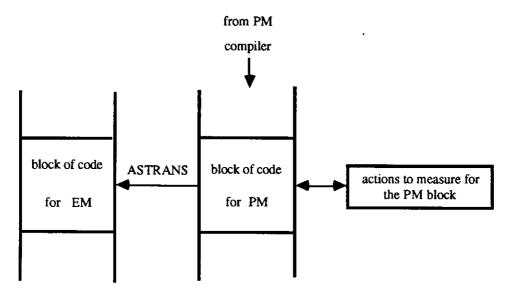

- 2. Otherwise, we have an *invalid mapping*. In this case, the assembly code of the PM has to be translated to the assembly code of the EM (see Figure 1.4). The complexity of the translation depends on similarities between instruction sets. Thus, additional overhead is introduced which depends on the number of EM instructions that have to be executed per PM instruction. However, the overhead is

Figure 1.4: PM to EM Block Translation

always smaller than for a simulator because only a few instructions have to be executed here per *simulated* (PM) instruction. This is the approach taken by [Chow86, Cort87b] (see Subsection 2.1.5).

Since we have always been able to find a valid mapping for the measurements that we have taken so far, the reader is referred to [Hugu87] for more information on the second alternative.

The size of the block and the interception code depends on the type of measurements that are being performed. Measurements can be classified into the following three types:

- I Measurements that are independent of the order of execution of the instructions. Examples are: opcode frequency, addressing modes distribution, register usage, memory traffic caused by local scalar variables, traffic caused by register saving and restoring with static policies.

- II Measurements that are dependent on the sequence of instructions executed, but independent of the state of the machine. In this case, the measurements do not depend on the values that are being computed during program execution. Examples are: frequency of pairs of opcodes, nested stack depth, branches taken or not taken, number of instructions executed between branches, traffic caused by register saving and restoring with dynamic policies, traces of instruction addresses.

- III Measurements that are dependent on the state of the machine. In this case, the function that is collecting the measurements needs to access the values computed during execution. Examples are: memory addresses generated for data, distribution of operand values for the multiplier, branch distances.

For measurements of Type III, each EM block corresponds to only one PM instruction because the PM state has to be updated after the EM instructions (associated with a PM instruction) have been executed. Since our measurements are of Types I and II and the complexity of BKGEN for measurements of Type III is greater than the one for the former types, we concentrate our attention on BKGEN for measurements of Types I and II. The reader is referred once more to [Hugu87] to find more information on BKGEN for measurements of Type III.

For measurements of Types I and II, the block corresponds to a basic block (as defined in Subsection 2.1.3). The advantage of grouping the PM instructions in a block is that the overhead caused by the EM instructions which are collecting the measurements is reduced since these EM instructions have to be executed once per PM block rather than once per PM instruction.

For measurements of Type I, the interception code consists of incrementing a counter associated with the block number, because it is only necessary to know how many times each block has been executed. (The order of instructions or blocks is not significant.) When the program finishes its execution, the number of occurrences of each event is computed as the product of the number of executions of each block by the number of event occurrences per block (given by the actions file). The use of this scheme for measuring the frequency of executed instructions for new machines was proposed by Weinberger [Wein84].

For measurements of Type II, the interception code consists of a call to a measurement function. This function can either (a) produce an execution trace of the blocks or (b) compute the measurements during program execution. The selection between these alternatives depends on the specific measurements and the overhead associated with their processing per block. Our experience with BKGEN has shown that it is more efficient to perform the measurements during program execution (in-line) due to the large overhead for writing a file of several Mbytes and the amount of disk space required for it; this case is shown in Figure 1.5.

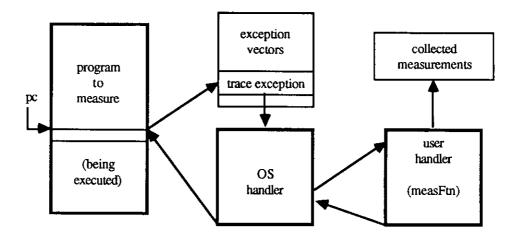

To estimate the overhead introduced by the different alternatives we have counted the number of executed instructions in the SORT program.<sup>4</sup> As we will show in Subsection 2.1.5, this can be considered the simplest type of measurement and, therefore, the observed overhead is the minimum overhead introduced by the different measurement techniques. The overhead generated is 1.5 times its normal execution time when the interception code only counts the number of times that a block has been executed, 8.4 times when the measurements are performed in-line, and 11.5 times when the sequence of block numbers is written to a file [Hugu87]. In contrast, the same measurement using the UNIX ptrace system call and implementing the tracer as an exception handler produces an overhead of 1,540 and 540 times, respectively.

To have a correct and successful execution of the measured programs, the interception code must not change the state of the EM (i.e., the registers, the condition codes, etc.).

<sup>&</sup>lt;sup>4</sup>Note that this is a Type I measurement. The reason for performing this measurement as Type II is only to estimate the overhead introduced.

Figure 1.5: Gathering Type II Measurements with BKGEN

The reader is referred to [Hugu87] to see how this is done on VAX-11.

The overhead introduced for the Type I measurements is very small—only a few instructions to increment a counter while preserving the machine state per block. For Type II, the overhead depends on the measurements that are being performed. However, since the measurement function is called only once per block and the events to be measured are given directly by the actions file, the overhead is always substantially smaller than for a simulator. For instance, the overhead to measure the RSR traffic generated by the static and the dynamic RSR policies is, on the average, 30 times the normal program execution.

In conclusion, the block-and-actions generator lets the designer measure many of the same events that can be measured by a simulator, an emulator, or a step-by-step instruction tracer. The effort to develop this new tool is not greater than the effort to develop a simulator, an emulator, or an instruction tracer. Since BKGEN directly executes machine code for the machine on which the measurements are performed, the execution time for obtaining measurements that do not depend on the machine state is significantly smaller than the execution time required to simulate the same program. Thus, for these types of measurements the designer can obtain meaningful dynamic characteristics of typical programs.

### 1.3 Programs Measured

In this section we first review some of the *standard benchmarks* that have been used to perform architectural evaluations and comment on why we do not use them. Afterwards, we present the *large typical programs* that we have selected to perform our evaluations.

In many cases the programs used as benchmarks are either small specific programs, such as the Ackermann's function [Wich76], LINPACK [Garb77], the Hanoi Towers, the Quicksort, the Fibonnacci Numbers, the Erastothenes Sieve [Gilb81], and the Puzzle Program [Beel84], or synthetic programs that either reflect some high-level language characteristics, such as the CFA benchmarks [Full77] and Dhrystone [Weic84], or measure some architecture characteristics, such as Whetstone [Curn76]. Programs of the first type are too small to be considered typical of any real system behavior, while those of the second type can only be representative of the characteristics considered in their design.

Our first measurements on several of the above-mentioned programs show that the results obtained from benchmarks might not be representative of real system behavior [Hugu85a]. For instance, the RSR traffic caused by Policy G for some of these benchmarks either is zero or has little variation from the traffic caused by Policy B. This is not the case when the large typical programs are measured. Some other authors [Levy82, Chow83, Colw85, Patt85b, Hitc86, Laru86, Wall88, Wong88] have also pointed out the limitations of these benchmarks for evaluating certain architecture features.

Table 1.1 shows some large programs used by some other studies. Small programs are enclosed in parentheses. Since only [Cort87a, Cort88] have used a fast simulator to perform their measurements, we have to assume that the simulation time required for the other studies was large since this is not reported in the papers and/or the number of different alternatives measured was small (to reduce the overall simulation time).

The large typical programs that we have selected to perform our measurements are written in C [Kern78]. C has been selected because it is widely used for system programming [Feue82], it has a type flexibility that allows to program system functions traditionally coded in assembler [Kern81, Post83], it has been used to implement UNIX, it can be used as an intermediate language for other block-structured languages such as ADA [Hill83], and it has been used to implement other languages such as LISP and PROLOG. No attempt is made in this work to generalize the measurements obtained for the C programs. The reader is referred to [Weic84] or [Huck83] for a comparison of the characteristics of different programming languages to C. The programs are:

- ASM. The UNIX assembler for VAX-11 (as), assembling one of the machine-independent Portable C Compiler modules (allo.s). ASM has 177 functions defined and executes 29,453 function calls.

- NROFF. The UNIX nroff word processor, formatting one third of the manual page entry for the FORTRAN 77 compiler. NROFF has 300 functions defined and executes 379,831 function calls.

- SORT. The UNIX sort program, sorting a file with 2,250 numbers. SORT has 68 functions defined and executes 142,448 function calls.

- **VPCC.** The UNIX Portable C Compiler (ccom) for VAX-11, compiling one of its machine-independent modules (allo.c). VPCC has 337 functions defined and executes 154,071 function calls.

| Reference  | Description                                                            |  |  |  |  |  |  |

|------------|------------------------------------------------------------------------|--|--|--|--|--|--|

|            | • First Pass of the Portable C Compiler                                |  |  |  |  |  |  |

| [Ditz82]   | UNIX word processor                                                    |  |  |  |  |  |  |

| 1          | • Second Pass of the PCC (generating PDP-11 code)                      |  |  |  |  |  |  |

|            | VLSI design ruler checker                                              |  |  |  |  |  |  |

| [Blom83]   | UNIX Portable C Compiler                                               |  |  |  |  |  |  |

|            | • (Puzzle and TAK—heavy recursive function)                            |  |  |  |  |  |  |

| [Tami83]   | UNIX Portable C Compiler                                               |  |  |  |  |  |  |

|            | • (Puzzle and Towers of Hanoi)                                         |  |  |  |  |  |  |

|            | LISP—Spice Lisp system from CMU                                        |  |  |  |  |  |  |

| [Laru86]   | • SLC—SPUR Lisp Compiler (based on Spice Lisp)                         |  |  |  |  |  |  |

|            | RSIM—circuit simulator                                                 |  |  |  |  |  |  |

| [Band87]   | UNIX system programs:                                                  |  |  |  |  |  |  |

|            | cat, comm, diff, echo, mv, nroff, pr, rm, and wc                       |  |  |  |  |  |  |

|            | Portable C Compiler for RISC                                           |  |  |  |  |  |  |

| [Cort87a]  | • NROFF—UNIX word processor                                            |  |  |  |  |  |  |

| [Cort88]   | • YACC—parser generator                                                |  |  |  |  |  |  |

|            | • LEX—lexical analyzer                                                 |  |  |  |  |  |  |

|            | AS—UNIX assembler for VAX-11                                           |  |  |  |  |  |  |

|            | • CCOM—main part of the UNIX Portable C Compiler                       |  |  |  |  |  |  |

| (17: 1.07) | COMPACT—adaptive Huffman code file compressor  FOR THE STREET COMPACT. |  |  |  |  |  |  |

| [Eick87]   | • EQN,TBL,NROFF—UNIX equation, table, and word processors              |  |  |  |  |  |  |

|            | • INDENT—C source program indenting program                            |  |  |  |  |  |  |

| İ          | PI—Pascal interpreter code translator                                  |  |  |  |  |  |  |

|            | • SORT—UNIX sort program                                               |  |  |  |  |  |  |

|            | • YACC—parser generator                                                |  |  |  |  |  |  |

|            | • CCAL—emulates a desk calculator                                      |  |  |  |  |  |  |

| [171071    | • Compare—compares 2 text files and indicates differences              |  |  |  |  |  |  |

| [Flyn87]   | • PCOMP—compiles PASCAL programs and generates P-code output           |  |  |  |  |  |  |

|            | • PASM—assembles the P-code output                                     |  |  |  |  |  |  |

|            | Macro—macro processor for SCALD                                        |  |  |  |  |  |  |

Table 1.1: Large Programs Measured by Some Other Studies

SPICE. A VLSI circuit simulator ("translated" to C from FORTRAN), simulating a unidirectional ratioless shift cell. SPICE has 1,171 functions defined and executes 175,567 function calls.

SPICE is a program that has different characteristics than the previous ones because it was originally written in FORTRAN. SPICE has fewer function calls, larger basic blocks, and heavy floating-point variable usage (see Section 4.3). Thus, we prefer to isolate this program from the rest. For this reason, in Section 1.1 we commented on the results for the average of the four programs (ASM, NROFF, SORT, VPCC) and for SPICE.

In some parts of this dissertation we use averages from our previous measurements. These are reported in [Hugu85a] and correspond to only three of the programs (NROFF, SORT, and VPCC). These measurements do not include the library functions which these programs use. However, we expect that the conclusions obtained would be the same if the library functions were included.

### 1.4 Organization of this Dissertation

The outline of the dissertation is the following: Chapter 2 presents a detailed summary of the work performed in this area (multiple-window architectures, register allocation and assignment, performance evaluation of new architectures, etc.) and of some related work that is not directly discussed in this dissertation (CISCs versus RISCs and cache memories versus registers).

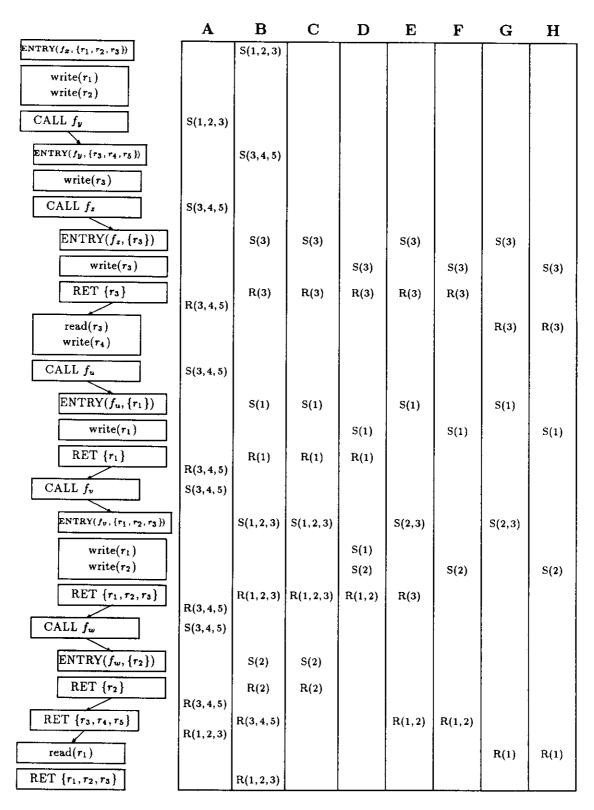

Chapter 3 presents the six architectural policies to reduce the RSR traffic as well as the implementation sketch for Policy G. The RSR traffic generated by these policies is compared with the RSR traffic generated by the standard Policies A and B when no optimizations are performed. Only one compiler is used to perform the evaluation, the Portable C Compiler, because similar results would be obtained with the other two.

Chapter 4 presents the two new intra-procedural RSR policies and compares them with the existing RSR policies (live-variable analysis and leaf-function optimization). All three compilers are used to evaluate these policies. The RSR traffic generated is also compared to the RSR traffic produced by multiple-window architectures.

Chapter 5 introduces our inter-procedural optimizer. First, the traffic reduction obtained by each optimization (for global scalar traffic, for the return-address traffic, and for RSR traffic) is discussed separately. Afterwards, the independent optimizations are put together and the optimal partition of the general-purpose register set is evaluated. Only one compiler is used to perform the inter-procedural evaluations, the GNU C Compiler, since it is the one which generates the least overall data memory traffic when intra-procedural optimizations are performed.

Finally, Chapter 6 summarizes the contributions of this dissertation and suggests areas for future work.

# Chapter 2

# Previous and Related Work

#### 2.1 Previous Work

This section presents the previous work that has been performed in the following areas:

- Multiple-window architectures.

- Single-window architectures.

- Register allocation and assignment and RSR policies.

- Performance studies on register allocation.

- Performance evaluation of new architectures.

These are discussed in turn.

## 2.1.1 Multiple-Window Architectures

With recent technological advancements it is possible to have a large number of registers on a single chip [Site79a]. To reduce the register saving and restoring traffic multiple-window architectures have the large register file divided into register windows. Every time that a function is called, a new window is made available [Site79a, Dann79, Lamp82] so that no RSR has to be performed. When there are no more windows available (i.e., an overflow condition is detected), one or more windows must be transferred to memory [Tami83]. Similarly, when a function returns and there are no more windows in the register file (i.e., an underflow condition is detected), one or more windows have to be transferred back from memory. Windows might overlap to pass parameters through registers so that data memory traffic is further reduced [Patt82b].

In this section, we first describe the general organization of a register file with multiple windows. Second, we present three schemes to divide the register file into windows: fixed-size windows [Kate83], variable-size windows [Ditz82], and multi-size windows [Hugu85a].

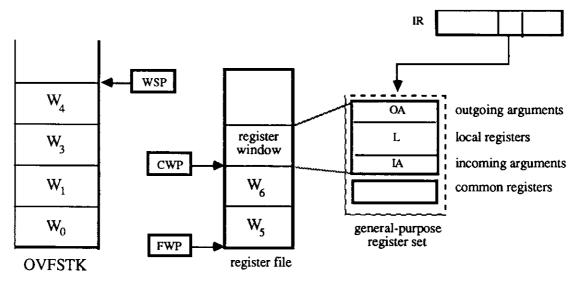

Figure 2.1: Multiple-Window Register Files

We comment on the drawbacks that fixed-size and variable-size windows have and how they are reduced by the use of multi-size windows and of a shift-register file. We also mention a different approach to reduce these drawbacks: the *dribble-back register file* [Site79a]. Finally, we discuss some evaluation studies that have been performed on multiple-window architectures.

Figure 2.1 shows the organization of a register file with multiple windows. The programmer (i.e., the compiler) sees the general-purpose register set divided into the following groups:

- A group of *common* registers to all the functions. The compiler has to preserve (if necessary) the contents of these registers to prevent them from being destroyed across function calls.

- A group of registers for the *incoming arguments* (IA) of the function. One of these registers contains the return address.

- A group of *local* registers. These registers are preserved across function calls (as well as the incoming registers).

- A group of registers for the *outgoing arguments* (OA) for the function that might be called.

The window size is defined as the number of new registers that are allocated per call. Thus, the size of the window is the number of local registers plus the number of overlapped registers (i.e., OA registers). In the figure we can also see the overflow stack, OVFSTK, where windows are transferred on overflow.

Most register file designs use fixed-size windows because of the simplicity in the implementation: C/70, RISC I and II, PYRAMID 90x, C1200, SOAR, SPUR, the LISP-

| Processor                               | Description                                              | References         |

|-----------------------------------------|----------------------------------------------------------|--------------------|

|                                         | 8 general-purpose registers                              | Ī                  |

|                                         | no overlapped/common registers                           |                    |

| C/70                                    | • register file size = 1024                              | [Kral80, BBN81]    |

| <b>'</b>                                | number of windows = 128                                  | (moles, BBRel)     |

| (BBN Computer Co.)                      | NO overflow exception detection                          |                    |

| , , , , , , , , , , , , , , , , , , , , | • 32 general-purpose registers                           | [Piep81, Fitz82]   |

|                                         | window size = 16                                         | [Laru82, Patt82a]  |

|                                         | overlapped registers = 6                                 | [Patt82b, Séqu82]  |

| RISC I & II                             | common registers = $10 \ (r\theta \equiv 0)$             | [Blom83, Kate83]   |

|                                         | • register file size = 128 + 10                          | [Patt83, Peek83]   |

| (Univ. of California,                   | number of windows = 7+                                   | [Pond83, Tami83]   |

| Berkeley—UCB)                           | circular buffer organization                             | [Patt84, Sher84]   |

|                                         | • variable-size windows                                  | [Ditz82, Bere87a]  |

| CRISP                                   | • registers mapped to memory                             | [Bere87b, Ditz87a] |

|                                         | • register file size = 32                                | [Ditz87b, Ditz87c] |

| (AT&T Bell Labs.)                       | • 7 special registers $(psw, pc,)$                       | [Diczoro, Diczorc] |

| (====================================== | • 64 general-purpose registers                           |                    |

|                                         | window size = 32                                         |                    |

|                                         | overlapped registers = 16                                |                    |

| Pyramid 90x                             | common registers = 16                                    | [PTC83, Raga83]    |

| 1 Jidilia sox                           | • register file size = 512 + 16                          | [1 1 Coo, reagaco] |

|                                         | number of windows = 15 <sup>+</sup>                      |                    |

| (Pyramid Technology)                    | circular buffer organization                             |                    |

| C1200                                   | • As Pyramid, but with 8 register files                  |                    |

|                                         | for fast context switching                               | [CEL85, Olle85]    |

| (Celerity Computing)                    | • 4096 registers                                         | [CDD00, Oncos]     |

| ( seeing somputing)                     | • 32 general-purpose registers                           |                    |

| SOAR                                    | window size = 8 (all overlap)                            | [Unga84, Samp85]   |

|                                         | 8 special regs. $(r16 \equiv 0; r17-r23 \text{ for OS})$ | [Samp86, Unga86]   |

|                                         | 8 common registers                                       | [Sampoo, Ongaoo]   |

| (UCB)                                   | • register file size = 64 + 16                           | [Adam85, Chen85]   |

| (00)                                    | • general-purpose registers as RISC II                   | [Gibs85, Hans85]   |

| SPUR                                    | • 15 floating-point registers                            | [Katz85, Ritc85]   |

|                                         | • 7 special registers                                    | [Tayl85, Vill85]   |

| (UCB)                                   | (psw's, pc's, reg. window ptrs.)                         | [Hill86, Tayl86]   |

| (001)                                   | • variable-size windows                                  | [Wood86, Borr87]   |

|                                         | • registers in the Execution Unit:                       | [1100deo, Dorror]  |

| Dragon                                  | 128-stack regs, 16 auxiliary, 12 constant                | [Atki87]           |

| Diagon                                  | • registers in the Instruction Fetch Unit:               | [Aukioi]           |

| (Xerox)                                 | 15-element stack of pc's and context ptrs.               |                    |

| (ACIOA)                                 | • register file size = 64                                |                    |

| LISP-Machine                            | window size = 8                                          |                    |

| DIOI -Machine                           | window size $= 6$<br>overlapped registers $= 4$          | [Aboa87]           |

| (Univ. of Miami)                        | circular buffer organization                             | [ [ADOGOT]         |

| SPARC                                   | • variable register file size = 40-520                   |                    |

| JI AIRC                                 | 32-general purpose registers                             | [Garn88]           |

| (Sun)                                   | window size = 16 (8 overlapped)                          | [ Garmoo]          |

| (3011)                                  | window size = 10 (o overlapped)                          | 1                  |

Table 2.1: Multiple-Window Processors

Machine, and SPARC (see Table 2.1;<sup>1</sup> this table also gives a detailed list of references for the reader interested in knowing more about these systems). The main drawback with fixed-size windows is the number of *unused* registers in the file. For instance, we have measured three C programs (the NROFF word processor, the Portable C Compiler for VAX-11, and the SORT program) and have shown that, on the average, RISC has 10.9 registers unused per function (for a window size of 16) and Pyramid has 26.8 (for a window size of 32) [Hugu85c]. These unused registers not only waste area in the chip, but also have to be saved and restored on overflow, on underflow, and on context switch.

Variable-size windows [Ditz82] assign per function the exact number of registers required for the variables selected for allocation. Thus, no unused registers are present in the file. Only two of the machines in Table 2.1 (CRISP and Dragon) use variable-size windows. Although variable-size windows utilize the register file more efficiently because the exact number of registers required is allocated, their implementation significantly increases the complexity of the processor: large register addresses are required in the instruction, two more machine instructions are required to execute a function call (one to allocate a window at function entry and a second to detect underflow after return), and more overhead is incurred to map a virtual register address to a physical register address [Hugu85a].

Although a multiple-window register file has been shown to be effective in reducing the memory traffic due to saving and restoring of registers in function calls/returns [Patt82a], the resulting register files have the following three drawbacks:

- 1. They use a large chip area in VLSI implementations [Henn84]. For instance, for RISC II [Kate83] the percentage of the chip area dedicated to register storage is 27.5% and to the decoders is 5.8%.

- 2. They increase the size of the context to be saved during context switching, since all the windows in use have to be saved [Henn84]. For instance, for the programs mentioned above, we have shown that, on the average, 70 registers have to be saved on context switching for RISC II and 211 for Pyramid [Hugu85c].

- 3. They increase the processor cycle-time due to the increase in the length of the data busses [Henn84, Patt85a]. This length is proportional to the size of the register file. For instance,

- Sherburne [Sher84] claims that the datapath cycle time increases with the square root of the register-file size.

- Ditzel et al. [Ditz87b] say that the access time for register files larger than 16 or 32 increases about 30% when the register-file size is doubled.

<sup>&</sup>lt;sup>1</sup>The calculation of the number of windows per register file requires some explanation. Let us consider, for instance, the 128-register file for RISC. Although the register file has exactly 8 windows (128 registers  $\div$  16 registers per window), the table indicates that it has only  $7^+$ . This is because the first window in the file has 22 registers allocated (16 locals + 6 incoming registers) and, therefore, the eighth window is going to cause an overflow condition.

Figure 2.2: 64-Shift-Register File with Three-Size Windows

That is, for small register files (16 or 32) the other components in the datapath determine the basic processor cycle time. However, for larger ones the access time to the register file is critical in determining the processor cycle time.

To reduce these drawbacks we have previously proposed the combination of two approaches [Hugu85a, Hugu85b, Hugu85c]:

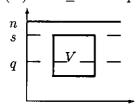

Multi-size windows: Instead of having only one window size (i.e., a fixed-size window), we have several sizes so that the best suited window is selected for the registers required by the function. Two-size windows (i.e., to have two window sizes) have also been proposed by Furht [Furh85, Furh88].

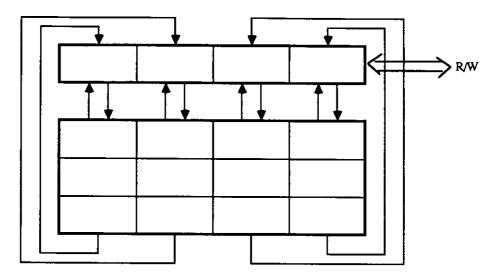

Shift-register file: This is a modification of the implementation of the circular-buffer register file [Kate83], which is used in most of the processors indicated in Table 2.1. Read and write operations are only performed on the registers of the top window. Registers are pushed (shifted down) when a function is called and popped (shifted up) when a function returns. In this case, the data busses are connected only to the top window so that the access time depends only on the register set, and not on the number of windows. For instance, Figure 2.2 shows a 64-register file with three-size windows of 4, 8, and 12 registers.

Multi-size windows differ from variable-size windows in that, by default, the smallest window is always allocated when the call is performed. Thus, if the callee does not require any more registers, no specific machine instruction is required at the callee to allocate a window. We have shown that when a 4-register window is allocated by default, 75% of the executed functions do not have to issue an instruction to increase the window size [Hugu85a]. Moreover, no explicit machine instruction is required to detect underflow after return. The standard return instruction detects an underflow condition when the largest window is not present in the register file.

Multi-size windows have essentially the same implementation complexity as fixed-size windows, but provide a better register utilization. For instance, a three-size window (4, 8, and 12) has, on the average for the three programs mentioned above (NROFF, SORT, and VPCC), 1.1 registers being unused; on the other hand, a fixed-sized window with 12 registers has 7.9. Moreover, for a 64-register file with three-size windows, the average number of registers saved per function call (0.06) doubles the average saved for a 512-register file with fixed-size windows of 32 (0.03) as used in PYRAMID and CELERITY. The implementation of multi-size windows produces, for the same overhead in register saving and restoring, a reduction in both the number of registers (windows) in the file and the size of the context to be saved. Therefore, two of the drawbacks (area required and context size) given by Hennessy [Henn84] are reduced.

Multi-size windows are also more suitable for general-purpose processors. Since different programming languages might use different window sizes, multi-size windows offer the flexibility of selecting the most appropriate one. For instance, measurements on C and PASCAL programs taken for RISC have shown that the most appropriate fixed-size window has 16 registers (with 10 local registers and 6 overlapped registers) [Patt82b], while measurements on Smalltalk programs taken for SOAR have shown that a window of 8 registers (with no local registers and 8 overlapped registers) is the most appropriate [Unga84]. Moreover, different application programs might also use different window sizes. For instance, our measurements have shown that a window size of 4 is large enough for 98% of the executed functions in NROFF, but for only 58% in the Portable C Compiler.

When the register file is implemented with shift registers, the area is further reduced and the access time becomes almost independent of the number of windows in the register file. It has been shown [Trem87] that the area for a 128-register file implemented as a circular buffer is 25% larger than the area required with shift registers and that the time of a READ operation has been reduced by 35%.

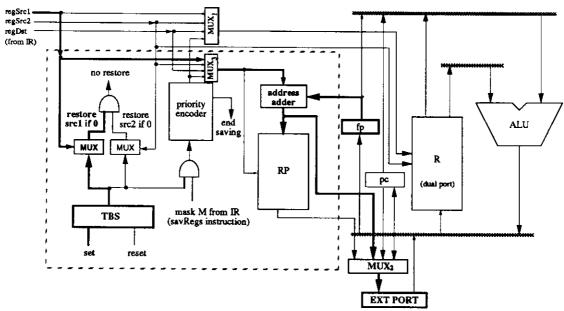

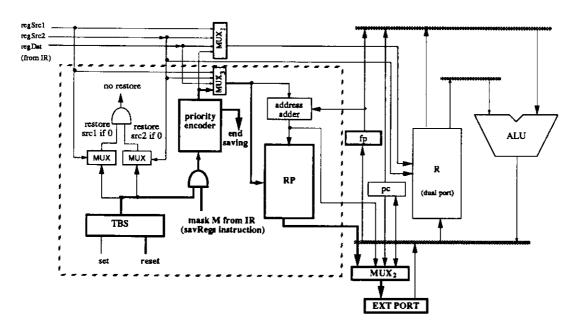

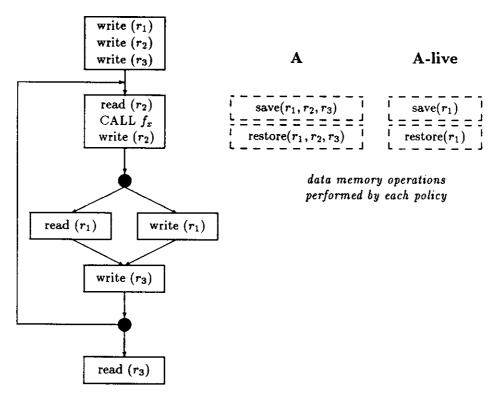

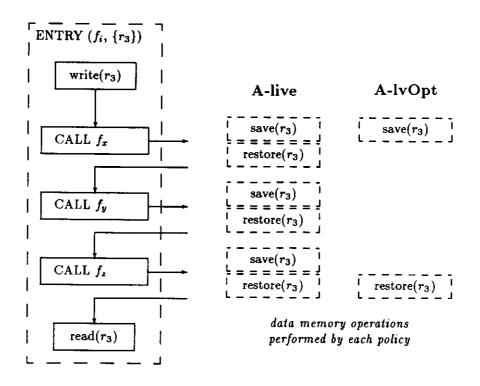

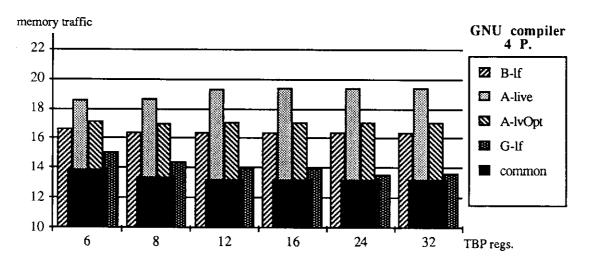

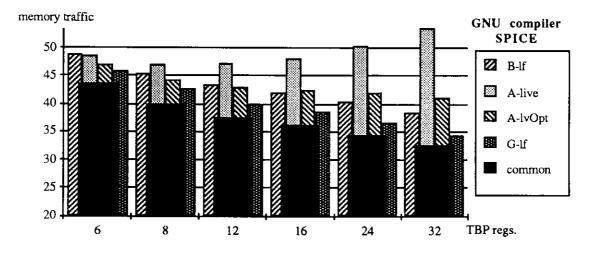

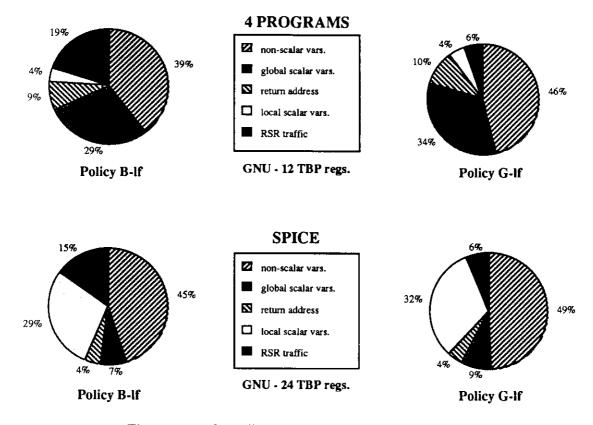

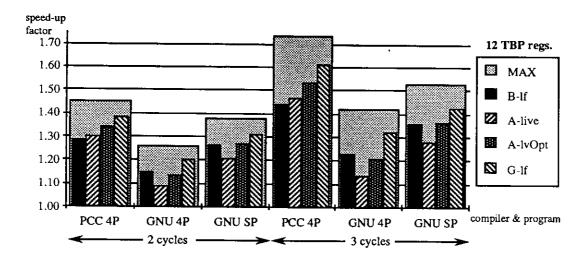

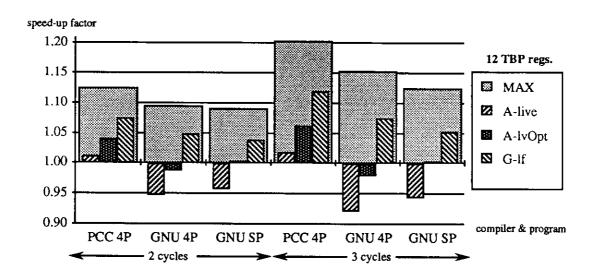

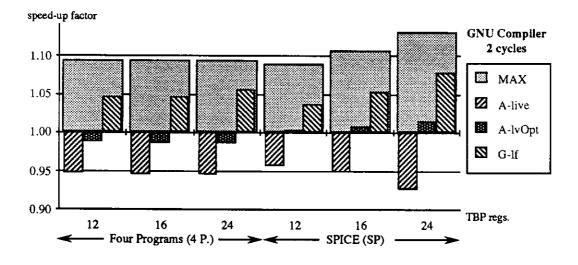

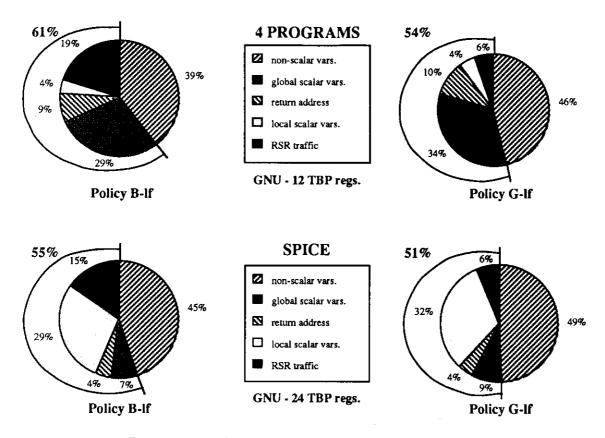

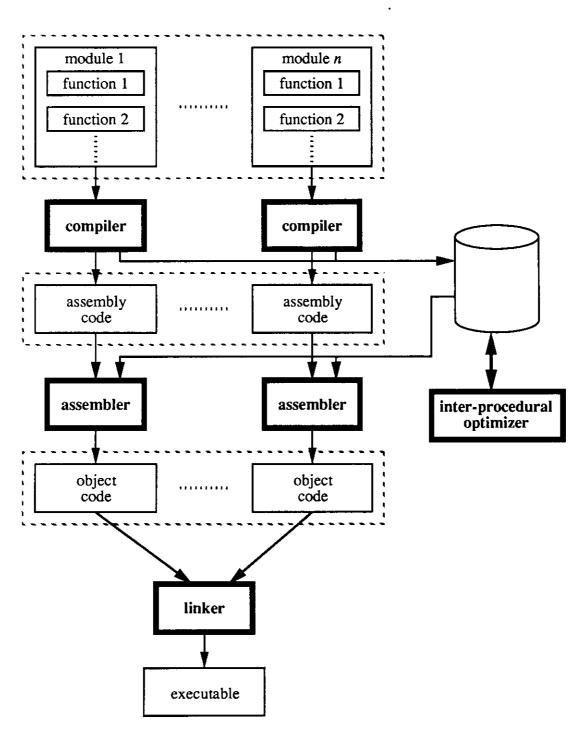

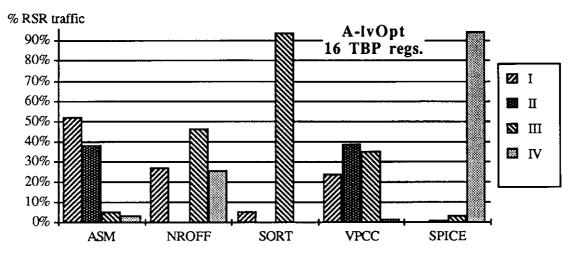

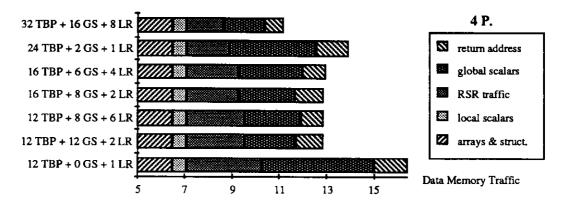

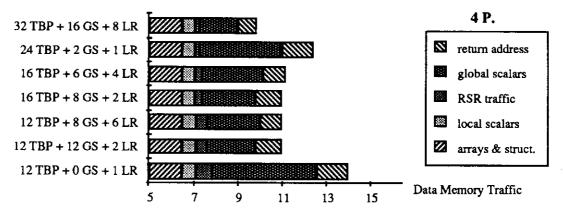

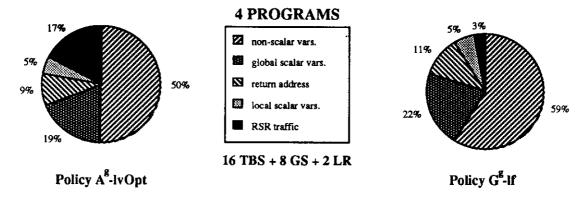

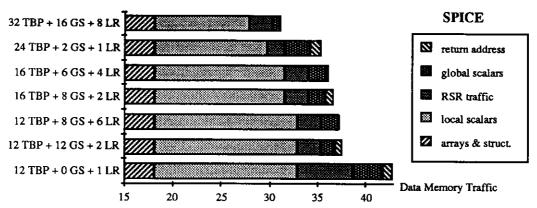

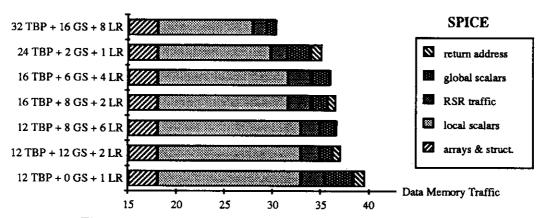

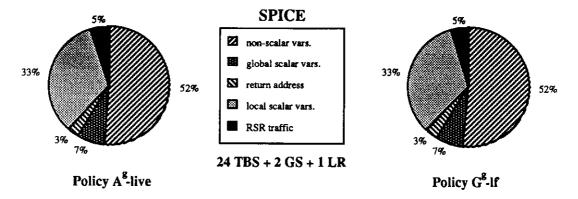

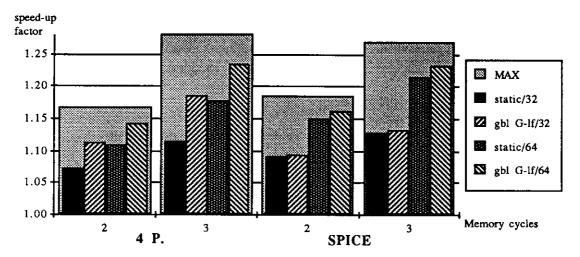

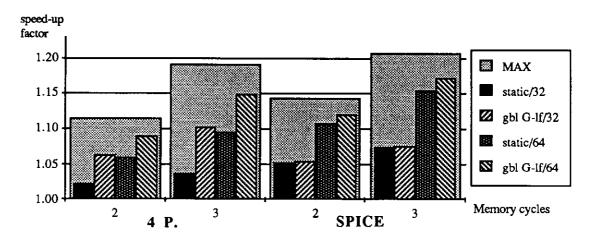

While multi-size windows reduce the three mentioned drawbacks, they do not completely eliminate these drawbacks. Thus, it is necessary to investigate alternative approaches to reduce the RSR overhead for the conventional single-window architectures. We will turn to these approaches in Chapter 3.